# ATARI HOME COMPUTER SYSTEM

# HARDWARE MANUAL

## COPYRIGHT 1982; ATARI, INC. ALL RIGHTS RESERVED

### TO ALL PERSONS RECEIVING THIS DOCUMENT

Reproduction is forbidden without the specific written permission of ATARI, INC. Sunnyvale, CA 94086. No right to reproduce this document, nor the subject matter thereof, is granted unless by written agreement with, or written permission from the Corporation.

Every effort has been made to ensure that this manual accurately documents this product of the ATARI Home Computer Division. However, due to the ongoing improvement and update of the computer software and hardware, ATARI, INC. cannot guarantee the accuracy of printed material after the date of publication and disclaims liability for changes, errors, or omissions.

## TABLE OF CONTENTS

| I•   | INTRODUCTION                                          |

|------|-------------------------------------------------------|

| II.  | DESCRIPTION OF HARDWAREII.1                           |

|      | A. ANTIC and CTIAII.1                                 |

|      | B. POKEYII.23                                         |

|      | C. SERIAL PORTII.25                                   |

|      | D. INTERRUPT SYSTEMII.28                              |

|      | E. CONTROLLERSII.30                                   |

| III. | HARDWARE REGISTERSIII.1                               |

|      | A. PALIII.1                                           |

|      | B. INTERRUPT CONTROLIII.1                             |

|      | C. TV LINE CONTROLIII.3                               |

|      | D. GRAPHICS CONTROLIII.4                              |

|      | E. PLAYERS AND MISSILESIII.9                          |

|      | F. AUDIOIII.12                                        |

|      | G. KEYBOARD and SPEAKERIII.15                         |

|      | H. SERIAL PORTIII.17                                  |

|      | I. CONTROLLER PORTSIII.19                             |

| IV.  | SAMPLE DISPLAY PROGRAMIV.1                            |

| v.   | HARDWARE REGISTER LISTSV.1                            |

|      | A. ADDRESS ORDER                                      |

|      | B. ALPHABETICAL ORDER                                 |

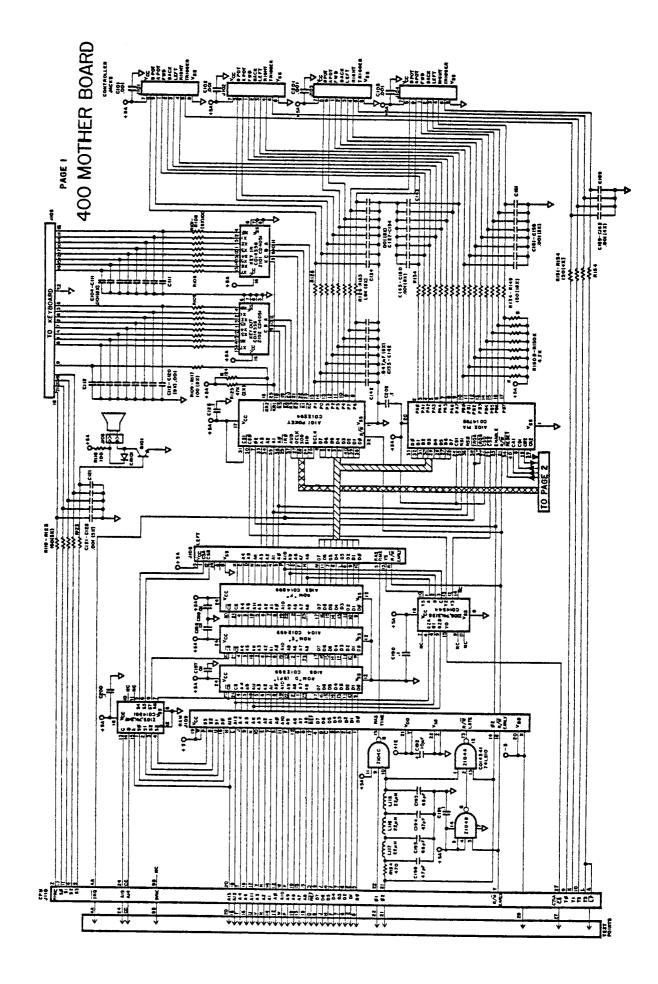

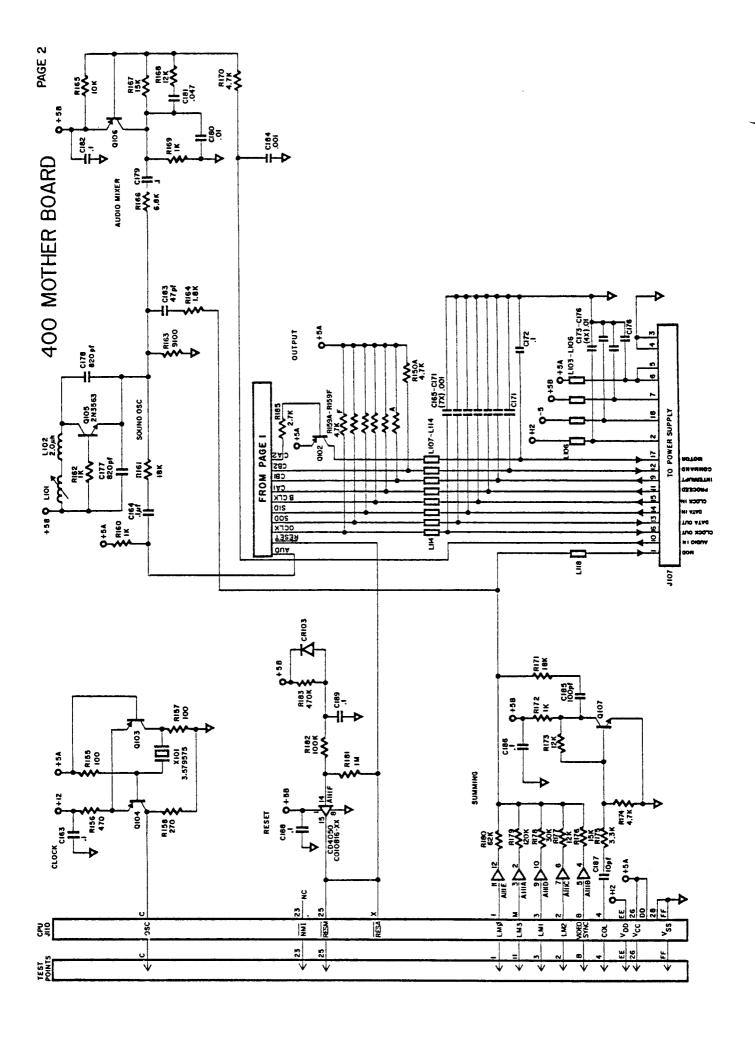

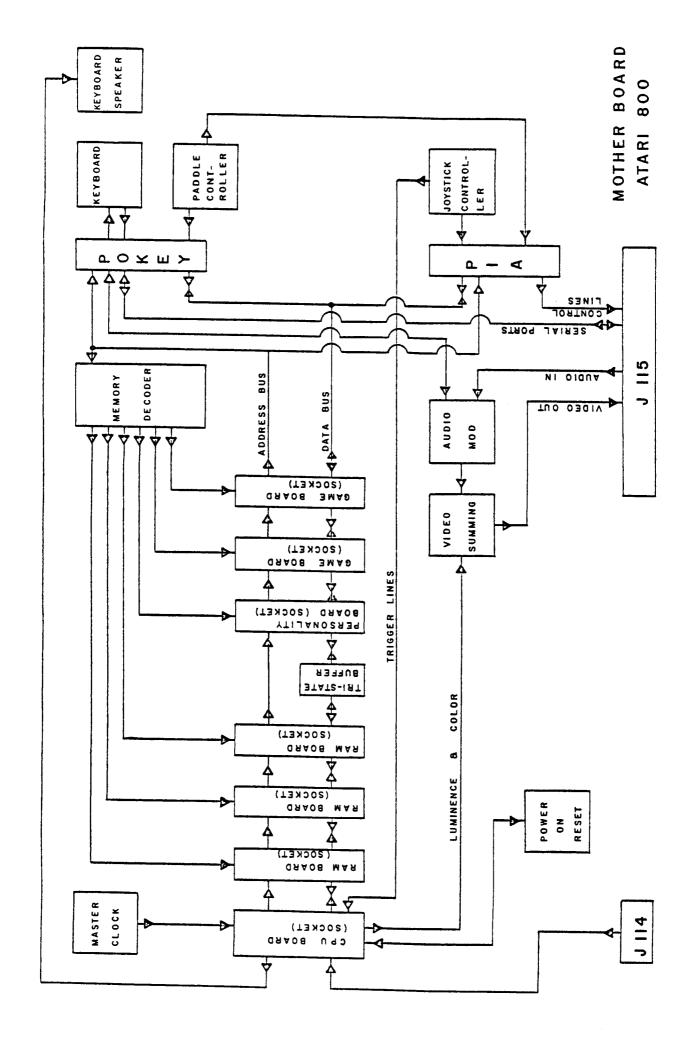

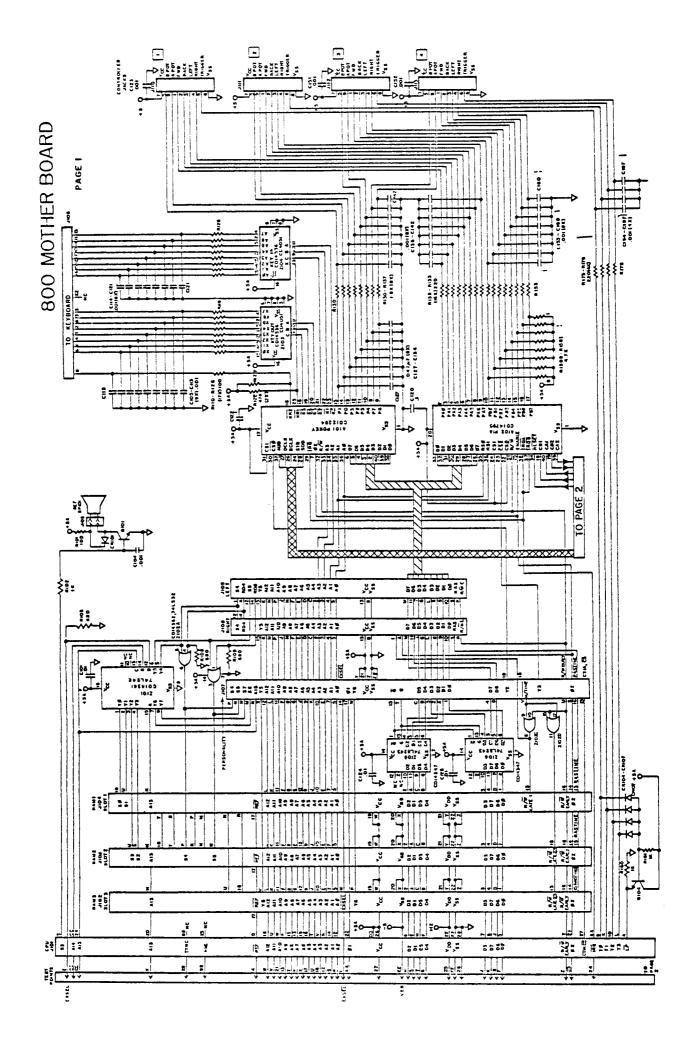

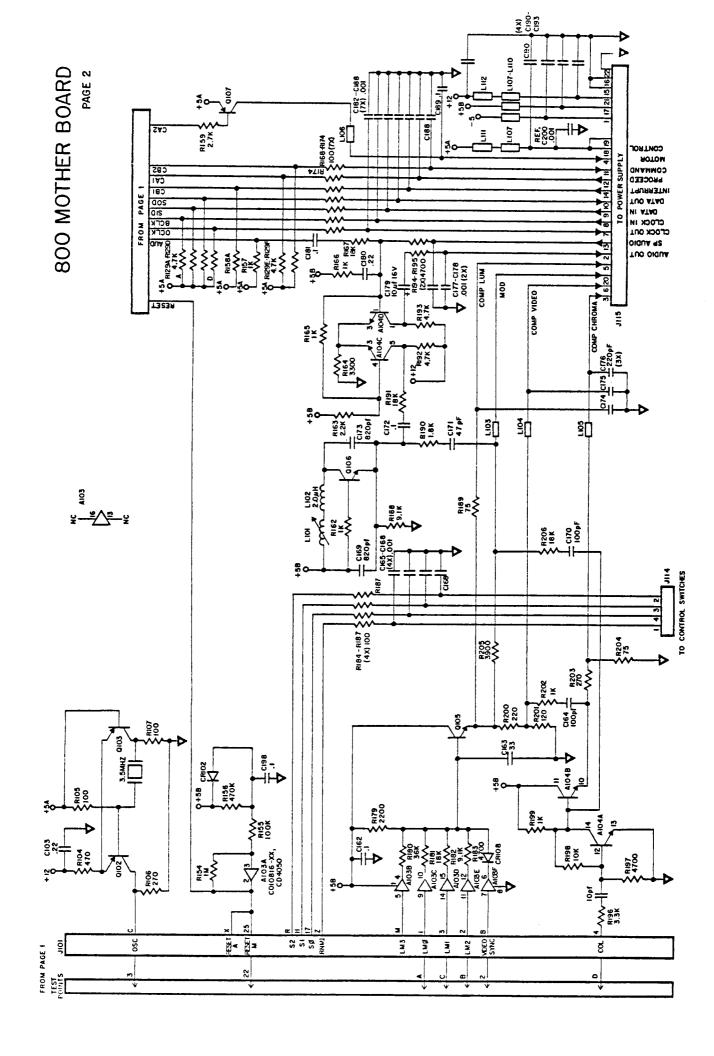

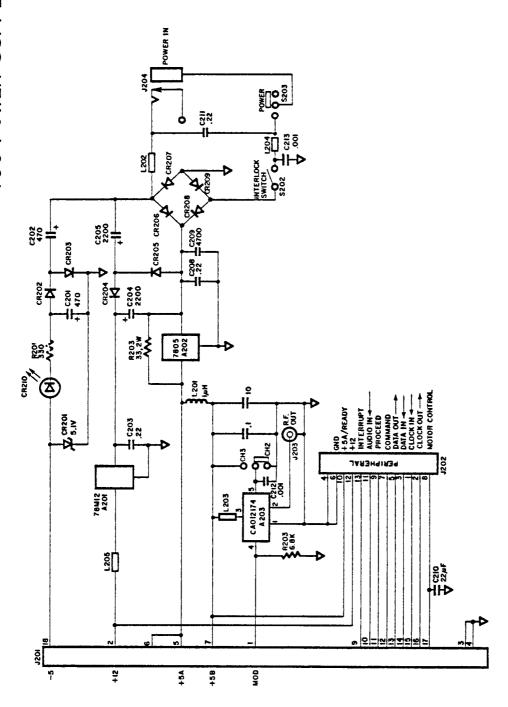

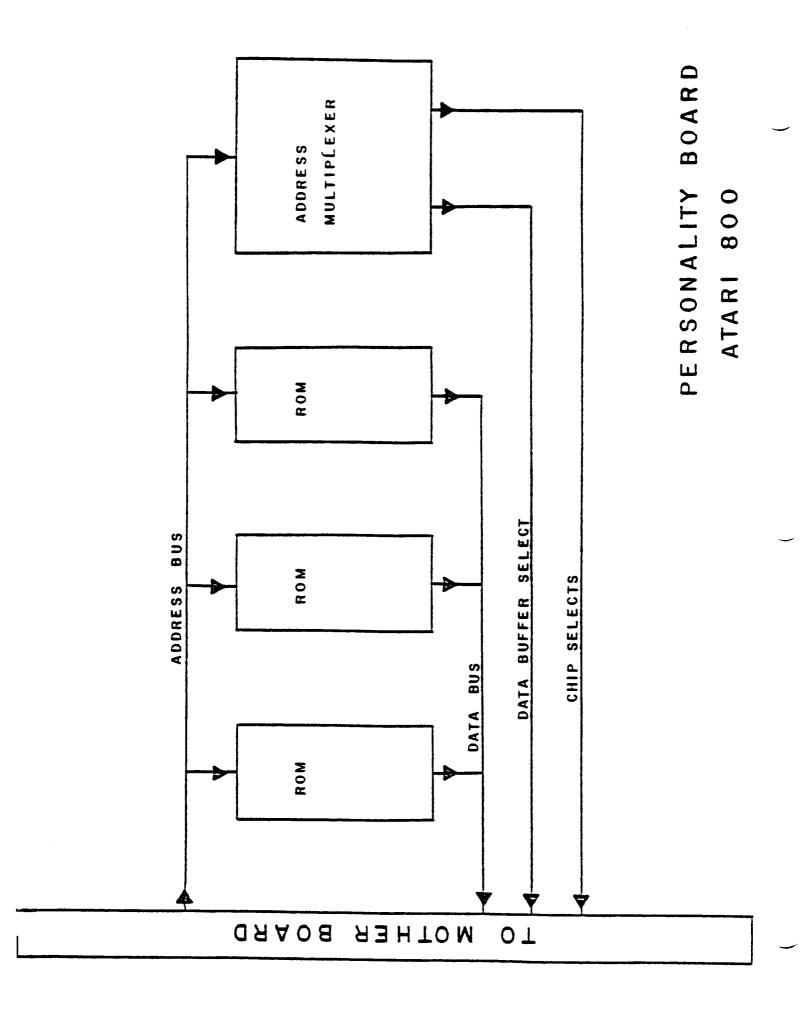

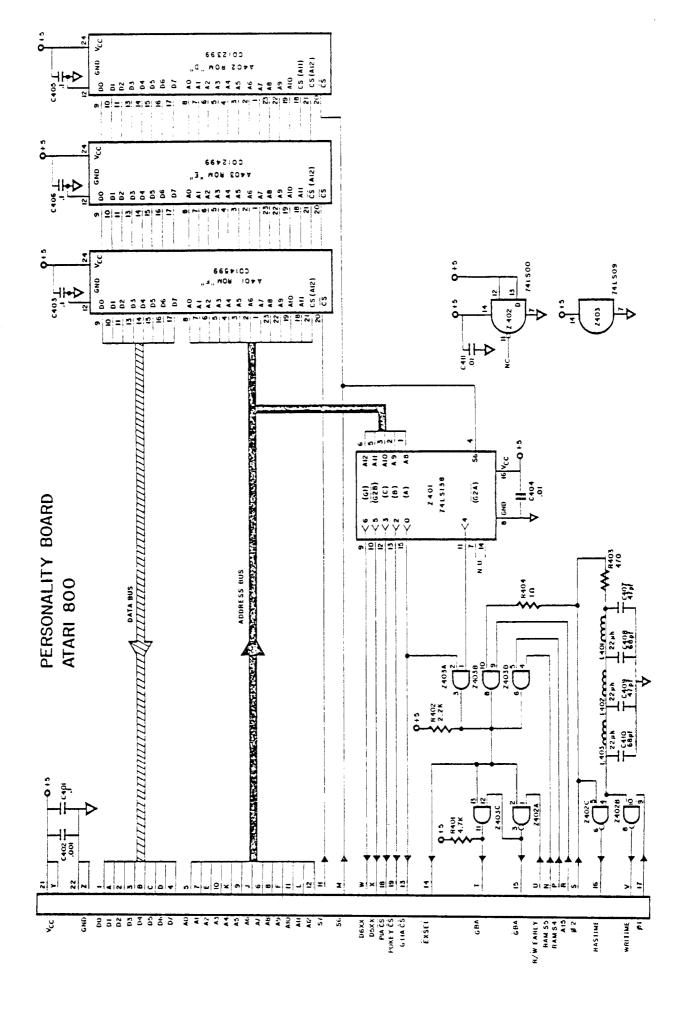

| VI.  | FIGURESVI.1                                           |

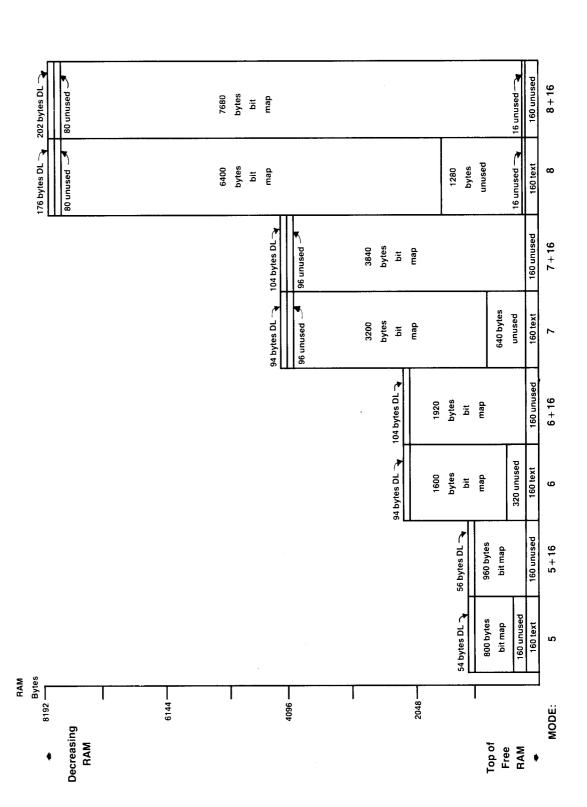

|      | A. MEMORY MAPVI.1                                     |

|      | B. NTSC and PAL DISPLAYVI.2                           |

|      | C. SCHEMATICSVI.3                                     |

|      | APPENDIX A: USE OF PLAYER/MISSILE GRAPHICS WITH BASIC |

|      | APPENDIX B: MIXING GRAPHICS MODES                     |

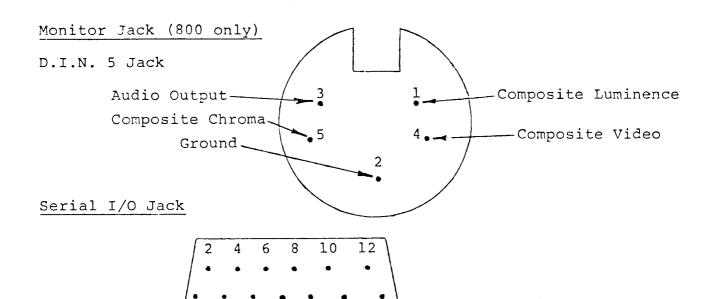

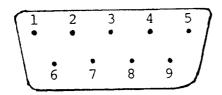

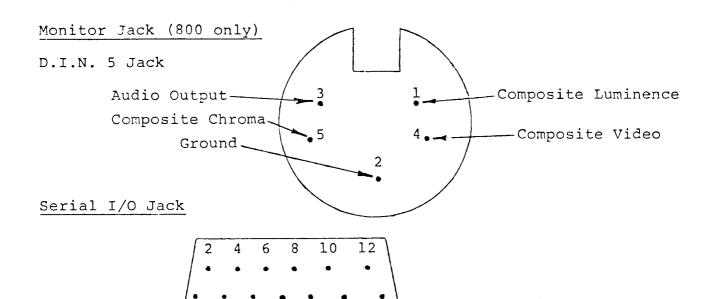

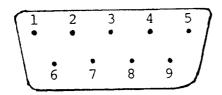

|      | APPENDIX C: PINOUTS                                   |

|   |  |  |  | ,        |

|---|--|--|--|----------|

| · |  |  |  |          |

|   |  |  |  |          |

|   |  |  |  |          |

|   |  |  |  |          |

|   |  |  |  |          |

|   |  |  |  | <i>.</i> |

|   |  |  |  |          |

|   |  |  |  |          |

### I. INTRODUCTION

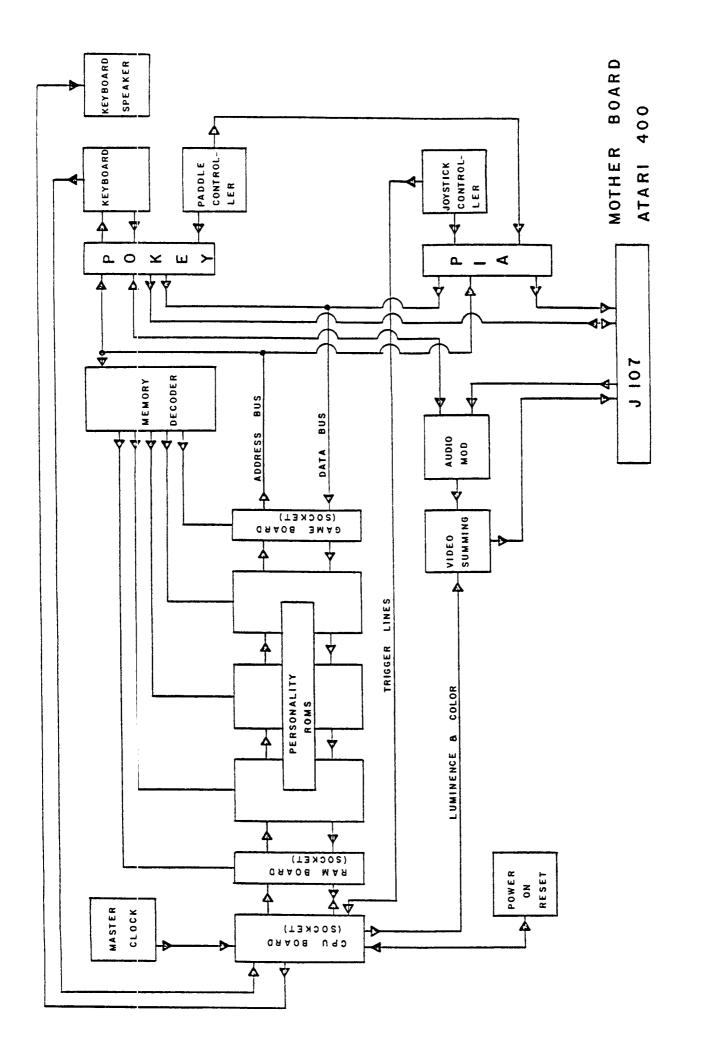

The ATARI (R) 800<sup>TM</sup> and ATARI 400<sup>TM</sup> Personal Computer Systems contain a 6502 microprocessor, 4 I/O chips, operating system ROM, expandable RAM, and several MSI chips for address decoding and data bus buffering. This manual is primarily intended to describe the 4 I/O chips in sufficent detail to allow experienced programmers to create assembly language programs, such as video games. All four Input/Output chips are controlled by the microprocessor by writing directly into their registers which are decoded to exist in microprocessor memory space just as RAM does. These I/O chips can also be interrogated by the microprocessor by reading similar registers.

Many registers are write only and cannot be read after they are written. In some cases, reading from the same address gives the value contained in a separate read only register. Some write only registers are strobes. No data bits are needed in this case since the presence of the address on the bus is what triggers the requested action. The usual convention is to use the STA (Store Accumulator) instruction for such registers. For example, STA WSYNC performs the wait for Sync function. STX (Store X) or STY (Store Y) would work just as well. In BASIC, a POKE could be used (the data could be anything). Reading a register is accomplished by using any of the load instructions (LDA, LDX etc.). In BASIC a PEEK would be used. When the hardware register names are defined in an equate list, the programmer can refer to the registers by name rather than using the addresses directly.

It is really not necessary for the programmer to know which I/O functions are performed by which of the 4 chips, however it does help in learning these functions.

This manual should be used in conjunction with the Operating System (OS) Manual, a 6502 programming manual, and the  $\underline{ATARI}$  400/800 Basic Reference Manual.

| CHIP NAME | FUNCTION |

|-----------|----------|

|           |          |

ANTIC

DMA(Direct Memory Access) control NMI(Non-Maskable Interrupt) control Vertical and Horizontal fine scrolling

Light pen position registers

Vertical line counter

WSYNC(wait for horizontal sync)

CTIA Priority control (display of overlapping objects)

Color-Lumimance control (colors and brightness assigned

to all objects including DMA objects from ANTIC) PLAYER-MISSILE objects (4 players and 4 missiles)

Graphics registers

Size control

Horizontal position control

Collision detection between all objects

Switches and triggers (miscellaneous I/O functions)

CHIP NAME FUNCTION

POKEY Keyboard scan and control

Serial communications port (bidirectional)

Pot scan (digitizes position of 8 independent pots)

Audio generation (4 channels)

Timers

IRQ (maskable interrupt) control from peripherals

Random number generator

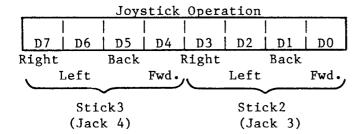

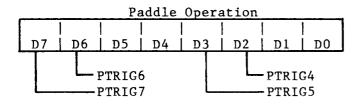

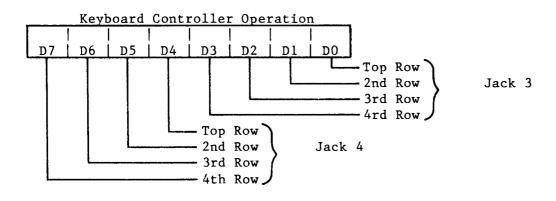

PIA Controller (Joystick) jacks read or write

Peripheral control and interrupt lines

IRQ (maskable) interrupt control from peripherals

Section II describes the hardware in some detail, including the various graphics modes. Section III lists the hardware registers one at a time, describing what each bit is used for. It is organized by functional groups (interrupts, graphics, audio, etc.). Section IV contains a sample display program. Section V contains various figures and block diagrams of the system. Sections VI and VII list the hardware registers in address order and alphabetical order. Section VII includes hex and decimal addresses, the OS shadow registers and the page numbers where more information can be found.

## II. DESCRIPTION OF HARDWARE

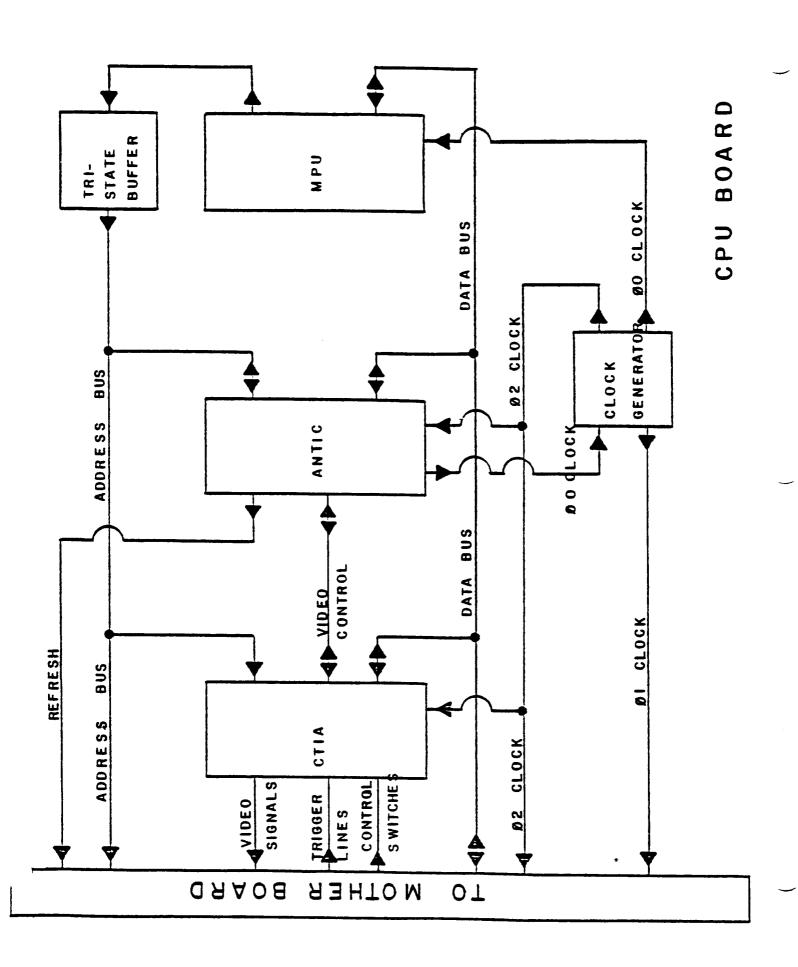

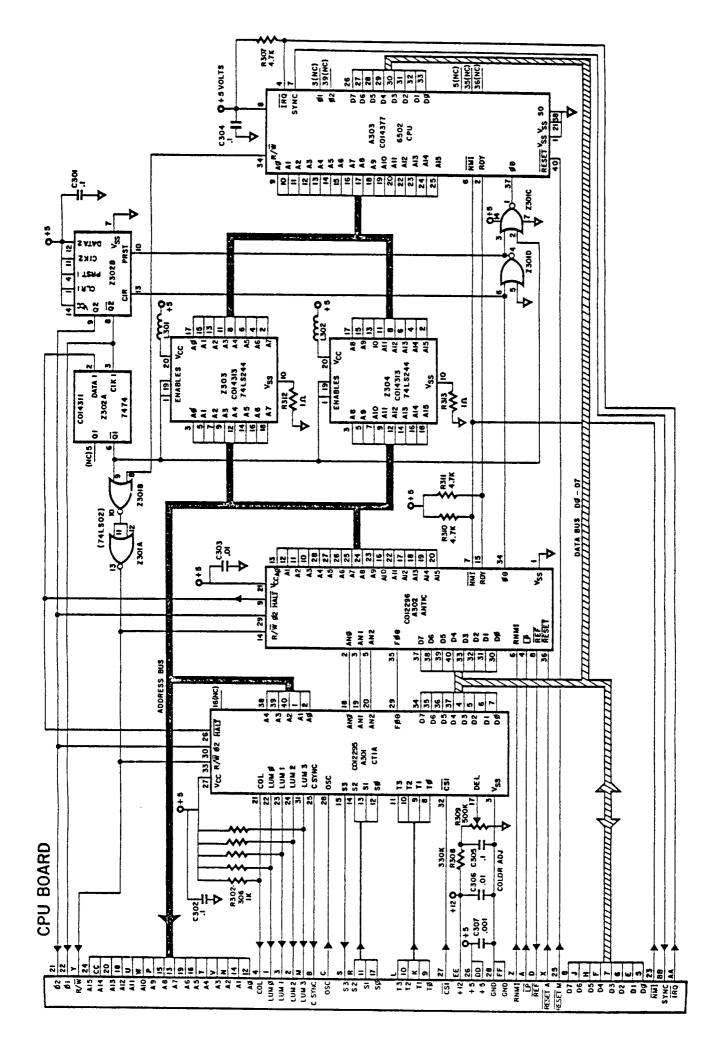

#### A. ANTIC AND CTIA

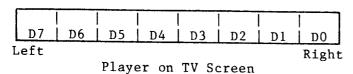

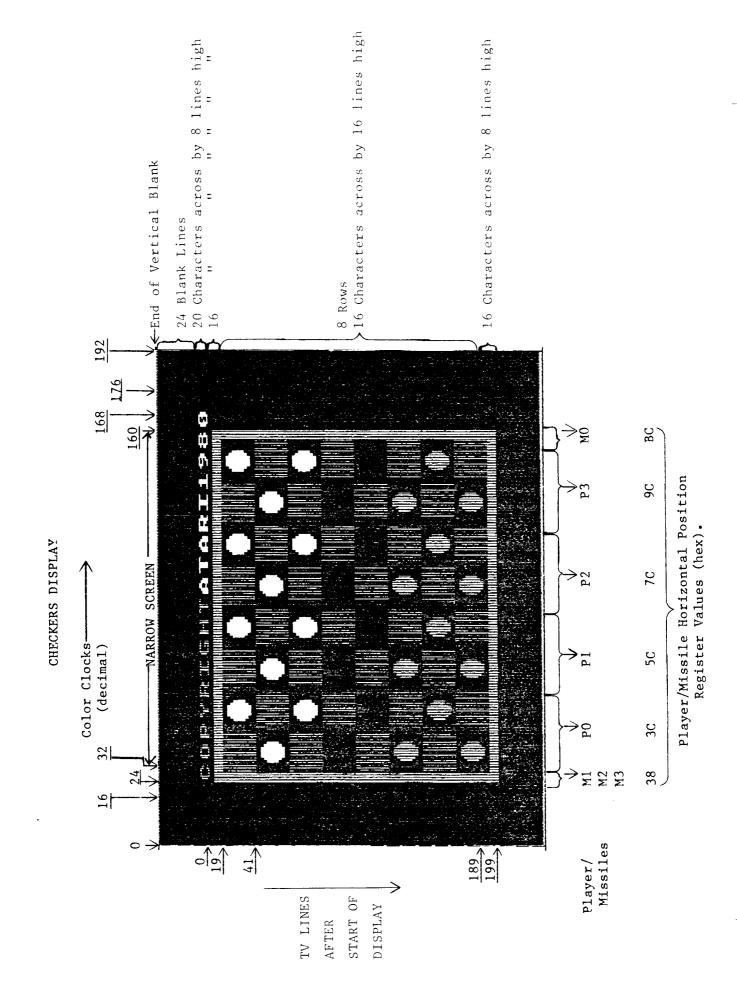

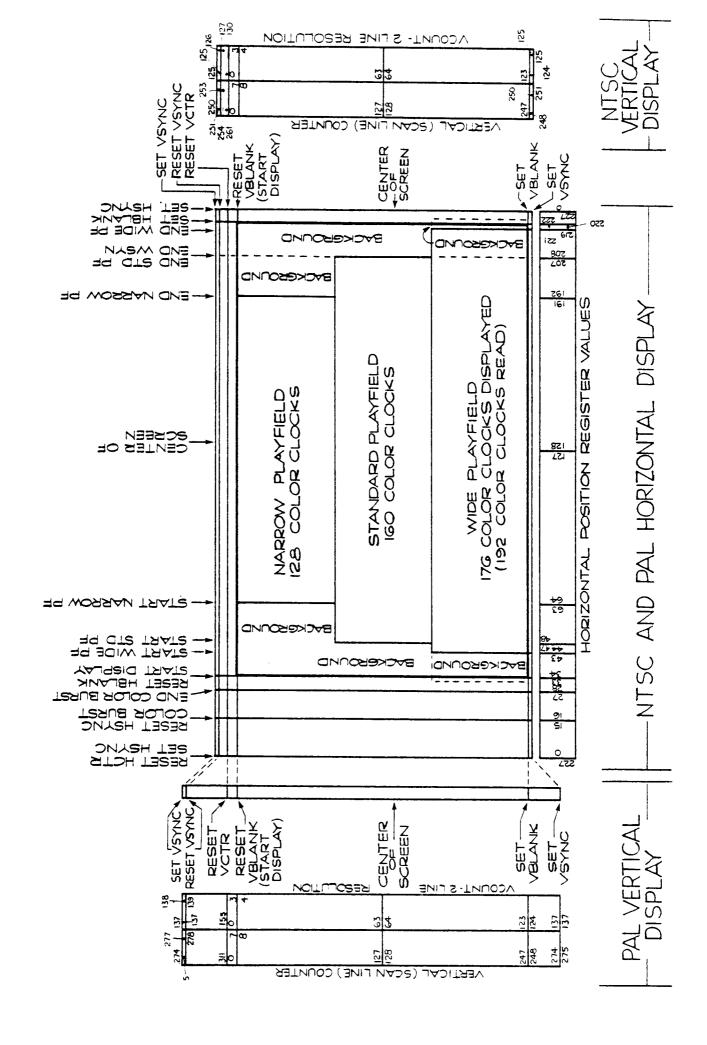

TV Display: The ANTIC and CTIA chips generate the television display at the rate of 60 frames per second on the NTSC (US) system. The PAL (European) system is different and is described in the section on NTSC vs PAL. Each frame consists of 262 horizontal TV lines and each line is made up of 228 color clocks, as shown in figure VI-3. The 6502 microprocessor runs at 1.79 MHz. This rate was chosen so that one machine cycle is equivalent in length to two color clocks. One clock is approximately equal in width to two TV lines.

In any graphics mode, the display is divided up into small squares or rectangles called pixels (picture elements). The highest resolution graphics mode has a pixel size of 1/2 color clock by 1 TV line. A sample display list is given in section IV.

The current TV line may be determined by reading the vertical counter (VCOUNT). This register gives the line count divided by 2. There are 262 lines per frame so VCOUNT runs from 0 to 130 (0 to 155 on the PAL system). The 0 point occurs near the end of vertical blank (see figure VI.5). Vertical blank (VBLANK) is the time during which the electron beam returns back to the top of the screen in preparation for the next frame. The Atari 800 does not do interlacing, so each frame is identical unless the program which is being executed changes the display. Vertical sync (VSYNC) occurs during the fourth through sixth lines of vertical blank (VCOUNT = hex 7D through 7F). This tells the TV set where each frame starts. After VSYNC, there are 16 more lines of VBLANK for a total of 22 lines of VBLANK. The display list jump and wait instruction (to be described later) causes the display list graphics to start at the end of VBLANK.

Operating System (OS): The ATARI 400/800 comes with a 10K Operating System (OS) in ROM. The OS affects some of the hardware registers, so it will be mentioned from time to time in this manual. Refer to the OS manual for more details. The OS descriptions in this manual apply to the version that was being distributed when this manual was written.

The OS supports most of the hardware graphics modes (BASICS, GRAPHICS, PLOT, and DRAWTO commands). The OS always displays 24 background lines after the end of vertical blank. This convention is used at Atari to compensate for television sets which overscan. Most TV's are designed so that the edges of the picture are cut off. This is fine for ordinary broadcasts, but with a computer it is essential for all important information to be displayed on the screen. It is fairly common for four to eight color clocks at the right or left edge of the picture to overscan. A TV set that has excessive overscan may have to readjusted to obtain a satisfactory display.

The OS uses 192 TV lines for its display and devotes the remaining 24 lines to overscan. It uses the standard display width of 160 color clocks. The hardware will allow displays of any length, but it is recommended that the standards be followed. The exception might be a border or other information which is merely decorative and not essential to use of the program.

OS Shadowing: Since many of the hardware registers are write-only and cannot be read the OS has a number of "shadow registers" in RAM. Every TV frame during vertical blank the OS takes the values in some of its shadow registers, and writes them out to the corresponding hardware register. The OS does attract color shifting on all of the color registers if ATRACT (on OS register) is negative. This is to prevent damage to the TV screen phosphors which can occur if the brightness is turned up too high and the same high-luminance display is left on for a long time. The OS also reads the joysticks and other controllers during vertical blank and stores the results in shadow registers, so that user programs do not have to include code to unpack the data. There are a few interrupt-related registers which the OS changes or reads during interrupt processing. Programs usually access the OS shadow registers instead of accessing the hardware directly. However, the OS shadowing can be disabled by changing the vertical blank and interrupt vectors (see OS manual).

WSYNC: In addition to a Vertical Blank Interrupt, which allows the Microprocessor to synchronize to the vertical TV display, this system also provides a Wait for Horizontal Sync (WSYNC) command that allows the microprocessor to synchronize itself to the TV horizontal line rate. This sync takes effect when the processor writes to an I/O location called WSYNC, whenever it desires horizontal synchronization. Writing to this address sets a latch which pulls to zero a pin on the microprocessor called READY. When READY goes to zero the microprocessor stops and waits. The latch is automatically reset (returning READY true) at the beginning of the next horizontal blank interval, releasing the microprocessor to resume program execution.

Object DMA (Direct Memory Access): The primary function of the Antic chip is to fetch data from memory (independent of the microprocessor) for display on the TV screen. It does this with a technique called "Direct Memory Access" or DMA. It requests the use of the memory address and data bus by sending a signal called HALT to the microprocessor, causing the processor to become "TRI-STATE" (open circuit) all during the next computer cycle. The ANTIC chip then takes over the address bus and reads any data it wishes from memory. Another name for this type of DMA is "cycle stealing". Once initiated, this DMA is completely and automatically controlled by the Antic chip without need for futher microprocessor intervention.

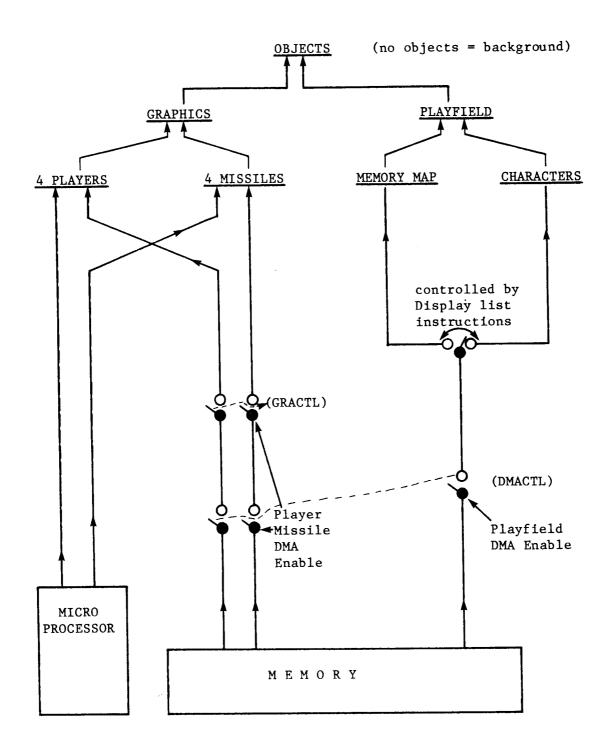

There are two types of DMA: Playfield and Player-Missile (see Figure II.2). The playfield DMA control circuit on the Antic chip resembles a small dumb microprocessor. By halting the main microprocessor it can fetch its own instructions from memory (the display list) addressed by its program counter(display list pointer). Each instruction defines the type (alpha character or memory map), and the resolution (size of bits on the screen), and the location of the data in memory which is to be displayed on the next group of lines.

In order to begin this DMA the main microprocessor must store a display list of instructions in memory, store data to be displayed in memory, tell the ANTIC where the display list is (initialize the display list pointer) and enable the DMA control flags on the ANTIC (DMACTL register).

In addition to the playfield DMA described above, the ANTIC chip simultaneously controls another DMA channel. This type of DMA addresses PLAYER-MISSILE graphics data stored in memory and passes the graphics data on to the CTIA chip graphics registers. This type of DMA (if enabled) occurs automatically, interspersed with the playfield DMA described previously. This PLAYER-MISSILE DMA has no display list or instructions, and is therefore much simpler than the PLAYFIELD DMA.

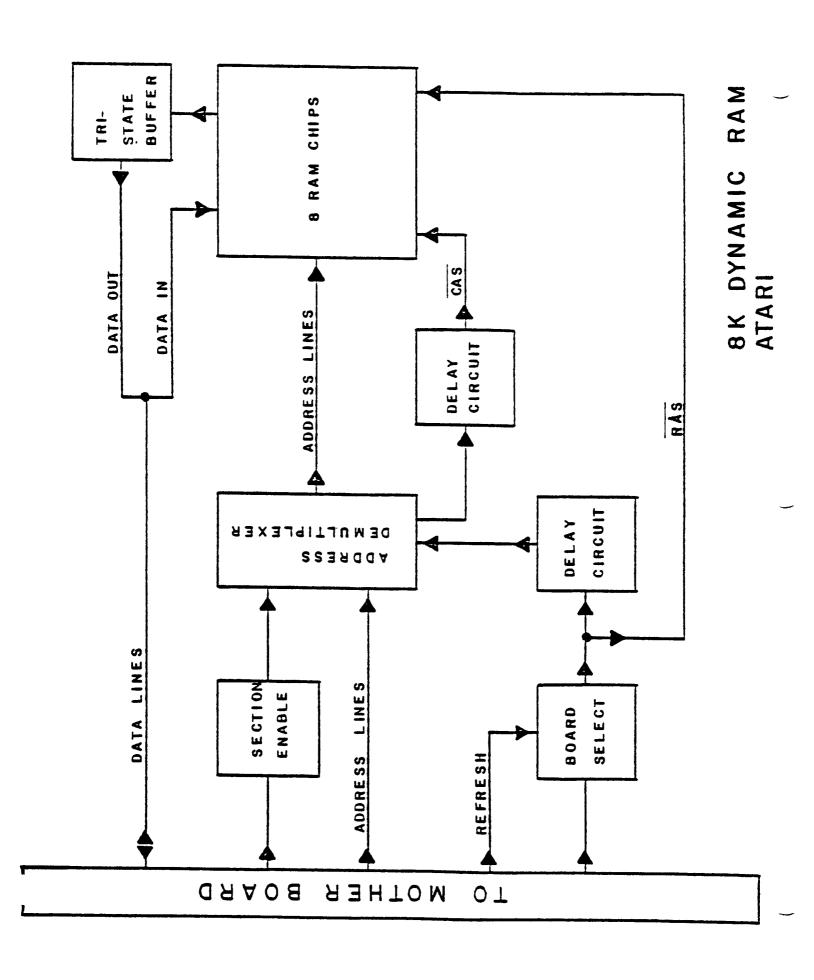

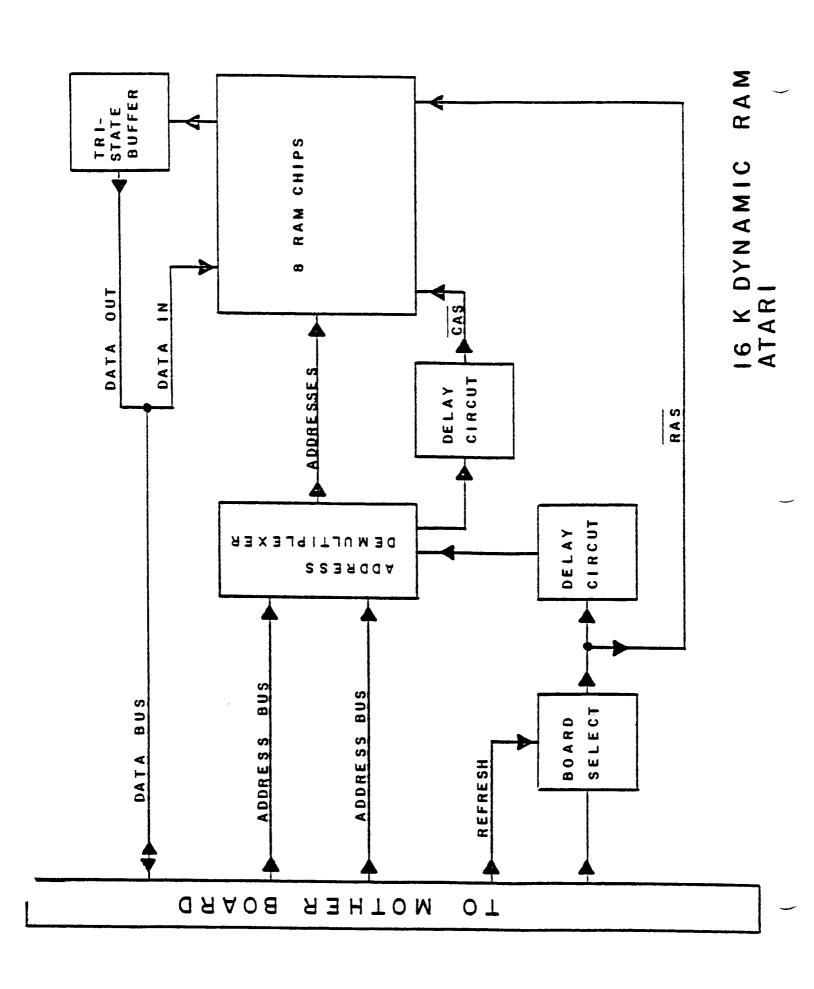

In addition to the two types of display DMA, the ANTIC chip also generates DMA addresses for the refresh of the dynamic memory RAM used in this system. This is also completely automatic and need be considered by the programmer only if he is concerned with real-time programming where an exact count of the computer cycles is important.

Color-luminance: A color-luminance register is used on the CTIA chip for each Player-Missile and Playfield type. Each color-lum register is loaded by the microprocessor with a code representing the desired color and luminance of its corresponding Player-Missile or Playfield type. As the serial data passes through the CTIA chip it is "impressed" with the color and luminance values contained in these registers, before being sent to the TV display. In areas of the screen where there are no objects the background color (COLBK) is displayed. The CTIA also does collision detection (to be described later).

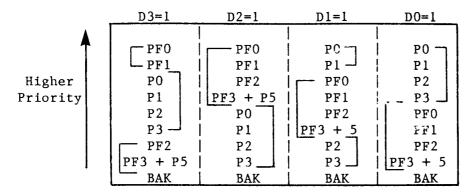

<u>Priority</u>: When moving objects, such as players and missiles, overlap on the TV screen (with each other or with Playfield) a decision must be made as to which object shows in front of the other. Objects which appear to pass in front of others are said to have Priority over them. Priority is assigned to all objects by the CTIA chip before the serial data from each object is combined with the other objects and sent to the TV screen.

The priority of objects can be controlled by the microprocessor by writing into the control register PRIOR. The functions of the bits in this register are given in the table in the PRIOR register description in section III.

Players and Missiles: The players and missiles are small objects which can be moved quickly in the horizontal direction by changing their position registers. They are called players and missiles because they were originally designed to be used in games for objects such as airplanes and bullets. However, there are many other possible applications for them. The four player-missile color registers, in conjunction with the four playfield color registers and the background color register, make it possible to display 9 different colors at the same time.

Figure II.2 OBJECT DISPLAY SOURCES

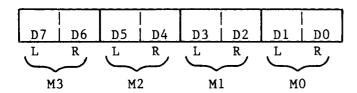

There are a total of four players and four missiles. The four missiles may be grouped together and used as a 5th player. These objects are positioned horizontally by 8 horizontal position registers (HPOS (X)). These registers may be reloaded at any time by the processor, allowing an object to be replicated many times across a horizontal TV line.

The shape of a player-missile is determined by the data in its graphics register (GRAF (X)). Players have independent 8 bit graphics registers. The four missiles have 2 bit registers (located within one address). These registers may also be reloaded at any time by the processor, although they are usually changed during horizontal blank time. The data in each graphics register is placed on the display whenever the horizontal sync counter equals the corresponding horizontal position register. The same data will be displayed every line unless the graphic registers are reloaded with new data.

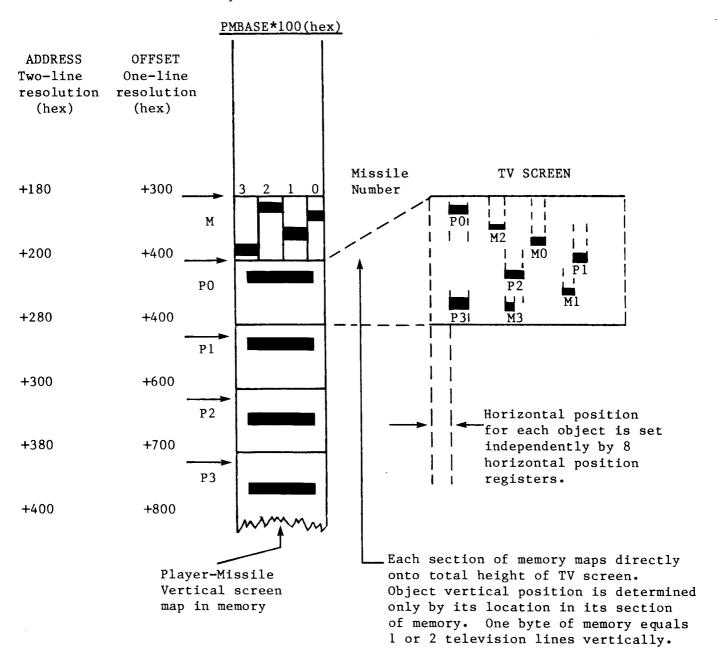

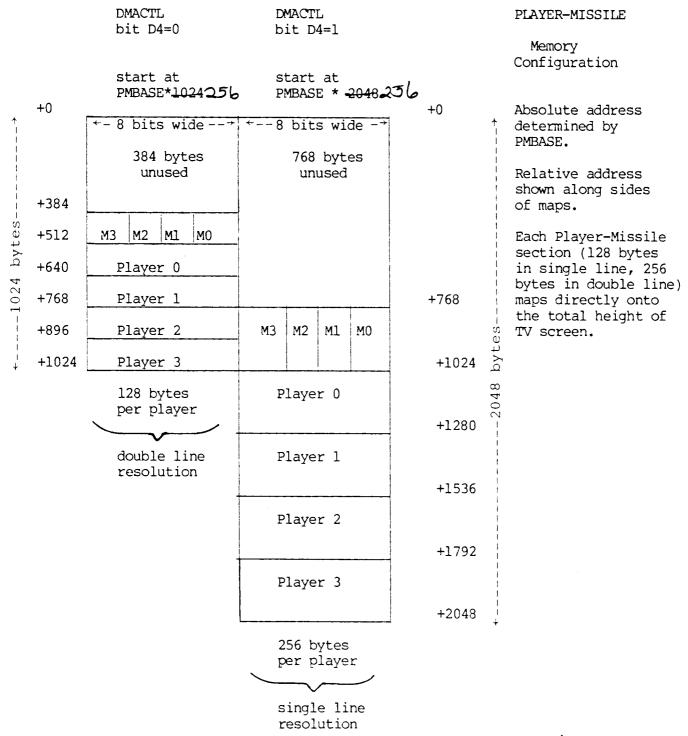

The player-missile graphic registers may be reloaded by the micro-processor (GRAF (X)), or automatically from memory with direct memory access (DMA) (see figure II.3). The programmer must place the object graphics in memory, write the player-missile base address (PMBASE), and enable player-missile DMA (DMACTL, GRACTL). The transfer of object graphics from memory to display is then fully automatic.

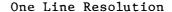

PMBASE specifies the most significant byte (MSB) of the address of the player-missile graphics. The location of the graphics for each object is determined by adding an offset to PMBASE \*256 (decimal). The bytes between the base address and the missile data are not used by Antic, so they are available to the programmer.

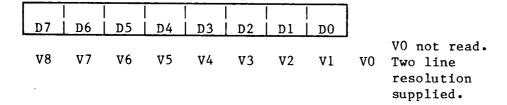

Only the five most significant bits of PMBASE are used with single-line resolution and the six most significant bits are used with two-line resolution. This means that the location of the graphics in memory is restricted to certain page boundaries. Two-line resolution means that each byte of data is repeated for two lines. (see DMACTL, bit 4). 640 (decimal) bytes (5X128) are required for two-line resolution and 1280 bytes (5x256) for one-line resolution.

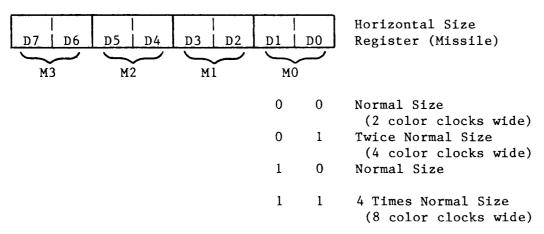

Each byte in the player graphics area represents eight pixels which are to be displayed on the corresponding line(s) of the TV screen. A l indicates that the player's color-lum is to be displayed in that pixel. The graphics may be anything, not just rectangles like the ones in figure II.3. The player graphics may fill the entire height of the screen or they may be only a couple of lines high if the rest of the display data is all 0's. Each byte in the missile display also represents eight pixels, two pixels for each missile. Each pixel may be 1, 2, or 4 color clocks, and is determined by the SIZE registers.

Playfield: Playfield is always generated by DMA. There are four playfields, each identified by its own color-lum register and collision detection. Playfield is generated by two different DMA techniques: memory map and character. Both methods provide lists of instructions in memory, independent of the player-missile generation.

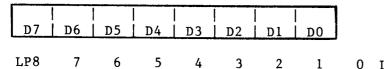

Player-Missile Base Address (PMBASE) = MSB of address. Resolution is controlled by bit 4 of DMACTL.

Figure II.2 PLAYER-MISSILE DMA

Unlike players and missiles, there are no horizontal position registers for playfield. Each player can only have one byte of display per line. Playfield, on the other hand, may require up to 48 bytes per line because it can fill the entire width of the screen.

There are three different playfield widths: narrow (128 color clocks), standard (160 color clocks), and wide (192 color clocks). The width is selected by storing into DMACTL. The advantage of a narrower width is that less RAM is required and fewer machine cycles are stolen for DMA. The OS graphics modes use the standard screen width.

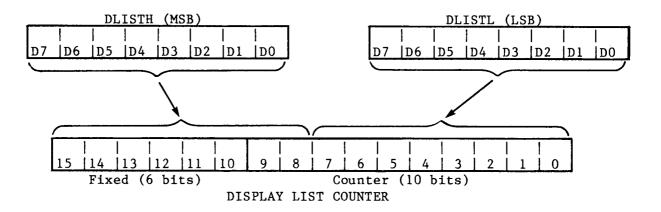

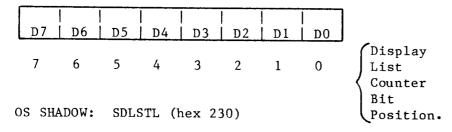

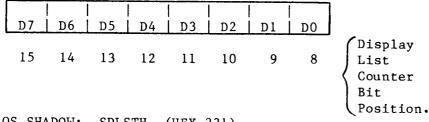

<u>Display List</u>: The display list is a sequence of display instructions stored in memory. These instructions are either one (1) byte or three (3) bytes long. The display list can be considered a display program, and the <u>Display List Counter</u> that fetches these instructions can be thought of as a display program counter. (10 bit counter plus 6 bit base register.)

The display list counter can be initialized by writing to DLISTH and DLISTL. (or OS shadow registers SDLSTH and SDLSTL). Once initialized this counter value is used to address the display list, fetch the instruction, display one (1) to sixteen (16) lines of data on the TV screen, increment the Display List Counter, fetch the next display instruction, and so on automatically without microprocessor control (see DLISTL and DLISTH). DLISTL and DLISTH should be altered only during vertical blank or when DMA is disabled (see DMACTL).

Each instruction defines the type (alpha character or memory map) and the resolution (size of bits on screen) and the location of data in memory to be displayed for a group (1 to 16) of lines. Each group of lines is called a display block.

THE DISPLAY LIST CANNOT CROSS A 1K BYTE MEMORY BOUNDARY UNLESS A JUMP INSTRUCTION IS USED.

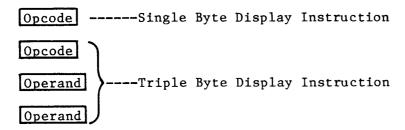

<u>Display Instruction Format:</u> Each instruction consists of either an opcode only, or of an opcode followed by two (2) bytes of operand.

The opcode is always fetched first and placed in the <u>Instruction</u> Register. This opcode defines the type of instruction (1 or 3 bytes) and will cause two more bytes to be fetched if needed. If fetched, these next two (2) bytes will be placed in the <u>Memory Scan Counter</u>, or in the Display List Counter (if the instruction is a Jump).

Display Instruction Register (IR): This register is loaded with the opcode of the current display list instruction. It cannot be accessed directly by the programmer. There are three basic types of display list instructions: blank, jump, and display.

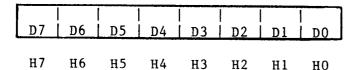

## Blank (1-byte) D7|D6|D5|D4| 0| 0| 0

This instruction is used to create 1 to 8 blank lines on the display (blackground color).

## Jump (3-bytes) D7|D6| X| X| 0| 0| 0| 1

This instruction is used to reload the Display List Counter. The next two bytes specify the address to be loaded (LSB first).

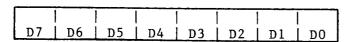

## Display (1 or 3 bytes) D7 D6 D5 D4 D3 D2 D1 D0

This instruction specifies the type of display for the next display block.

| HSCROL         | X                            | XX        | <u>×</u>       | XX    | XX    | ×             | XX           | _                 | XX      | _    | XX   |          | XX     |              | XX     | Horizontal Scrolling      |

|----------------|------------------------------|-----------|----------------|-------|-------|---------------|--------------|-------------------|---------|------|------|----------|--------|--------------|--------|---------------------------|

| VSCROL         |                              | <u> ~</u> | XX             | XX    | -     | ×             | X X X        | -                 | _       | XX   | XX   | _        |        | XX           | XX     | ertical Scrolling         |

| D MEM SC       |                              |           | _              | X     | XXX   | XXX           | X X X        | _                 |         |      |      | XX       | XX     | XX           | XX     | oad memory scan           |

| INST INTERRUPT |                              | -         | -              |       |       |               |              | XX                | XX      | XX   | XX   | XX       | XX     | XX           | XX     | isplay instruction int    |

|                |                              | _         | _              | _     | _     | _             |              |                   |         | _    | _    |          | _      | -            |        |                           |

| BLK 1          | 00                           | _         |                |       |       |               |              | 180               |         | _    |      | _        | _      |              |        | Blank 1 line              |

|                |                              | _         |                | -     | _     | _             |              |                   |         |      |      |          | _      | _            | _      | 1ank 2 1                  |

| 3-7            | _                            | _         | _              | —     | _     | _             |              | _                 |         |      | _    | _        | _      | _            | _      | Blank 3 thru 7 lines      |

| ∞<br>=         | 20                           | _         |                |       | _     |               |              | F0                |         |      |      | _        |        | _            | _      | lank                      |

| JMP            | 01                           | —         | —              |       |       | _             | <del>.</del> |                   |         |      |      |          |        |              |        | Jump (3 byte instruction) |

| JVB            | 41                           | _         | _              | —     | _     |               | _            | C1                |         | _    | _    |          |        |              | _      | mp & wa                   |

| (40,           | 2   1                        |           | 7              | 2   4 | 2   5 | 9             | 7            | <u>~</u>          | 6       | A 2  | B 2  | C2       | D 2 [] | _            | F2     | (also 3 byte)             |

| 7)             | $\frac{3}{1}$                |           | 3              | 3   4 | 3   5 | 9             | 1            | <u>~</u>          | 9       | A 3  | B3   | C3       | D3   ] | _            | F3     | •                         |

| " (40,4,8)     | 04 1                         | 4   2     | 24   3         | 7   7 | 4   5 | 79   7        | _            | _                 | 194     | A 4  | B4   | C 4      |        | 4            | 72     | Character Mode            |

| (40,4,1        | 5   1                        |           | 5              | 5   4 | 5   5 | 9             |              | $\frac{\infty}{}$ | 9       | A 5  | B5   | C5       |        | 2            |        | Instructions              |

|                | 6   1                        |           | 9              | 7   9 | 6   5 | 9             |              | 8                 | 9       | A 6  |      | 9        | _      | 9            |        |                           |

| 0,5,1          | 7   1                        |           | _              | 7   4 | 7   5 | 9             | 17           | <u>∞</u>          | 9       | A 7  |      | 7        |        | 7            |        |                           |

| P (40,4,8      | 8   1                        |           | <del></del>    | 8   4 | 8   5 | 9             | 1            | 8                 | 6       | A 8  | B8   | _        | _      | <del>-</del> |        |                           |

| 0              | 9   1                        | _         | 6              | 9   4 | 9   5 | 9             | 7            | <u>~</u>          | 6       | A 9  | B 9  | 6        | D 9 [] |              | F9     |                           |

| 0,4,           | A   1                        |           | <u> </u>       | A   4 | A   5 | 9             | 1            | <u>∞</u>          | 6       | AA   | BA   | _        |        | A            |        |                           |

|                | B 1                          |           | <u>—</u>       | B   4 | B   5 | 9             |              | <u>∞</u>          |         | AB   | BB   | <u>m</u> | _      | <u>B</u>     |        | Memory Map Mode           |

| 60,2,          | $c \mid 1$                   |           | $\overline{c}$ | C   4 | C   5 | 9             |              |                   | 96      | AC   | BC   | 22       | DC     | -            |        | truction                  |

| 60,4,          | D   1                        |           | <u> </u>       | D   4 | D   5 | 9             | _            |                   | 6       | AD   | BD   | _        |        | <u> </u>     |        |                           |

| (160,          | E   1                        |           | <u>교</u>       | E   4 | E   5 | 9             | _            | _                 | 9 区     | AE   | BE   |          | DE 1   | EE F         | E<br>E |                           |

| 20,2,          | $\mathbf{F} \mid \mathbf{I}$ |           | 드              | F   4 | F 5   | 9             | _            | <u>∞</u>          | 9 F     | AF   | BF   | CF       | DF 1   |              |        |                           |

|                |                              | 4         |                |       |       |               |              |                   | 1       |      | ,    |          |        |              | ,      |                           |

|                | Num                          | a)        | 0              | H     | lin   | a             | per          | o C               | 11      |      |      |          |        |              |        |                           |

|                | Numb                         | ber       | . of           | ပိ    |       | $\overline{}$ | 3ack         | gr                | puno    | +    | Play | fie      | 1 d    | type         | (s)    |                           |

|                | Num                          | ber       | 0              | Но    | rizc  | onta          | 11 c         | :e11              | s)<br>s | staı | ndar | мp       | 1dt}   |              | reen   | (1                        |

Figure II.3 DISPLAY INSTRUCTION OPCODES

Bit 7 of a display list instruction can be set to create a display list interrupt if bit 7 of NMIEN is set. The display list interrupt code can change the colors or graphics during the middle of the TV display. The type of interrupt is determined by checking NMIST. NMIRES clears NMIST. The current OS will vector through VDSLST (Hex 200 and 201) to the user's display list interrupt routine. See the OS manual for programming details.

Bits 5 and 4 of a display type of display list instructions are used to enable vertical and horizontal scrolling. The amount of scrolling depends on the values in the VSCROL and HSCROL registers (to be described later).

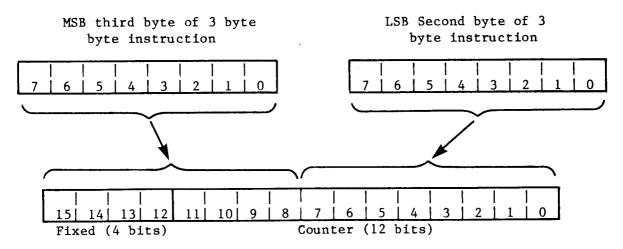

Memory Scan Counter: This counter is not directly accessible by the programmer. It is loaded with the value in the last 2 bytes of a 3 byte (non-Jump) instruction.

This counter points to the location (address) in memory of data to be directly displayed (memory map display) or to the location of character name strings to be indirectly displayed (character display).

A single byte instruction does not reload this counter. This implies a continuation in memory of data to be displayed from that displayed by the previous instruction. Since this counter really consists of 4 bits of register and 12 of actual counter, a continuous memory block cannot cross 4K byte memory boundaries, unless the counter is repositioned with a 3 byte Load Memory Scan Counter instruction.

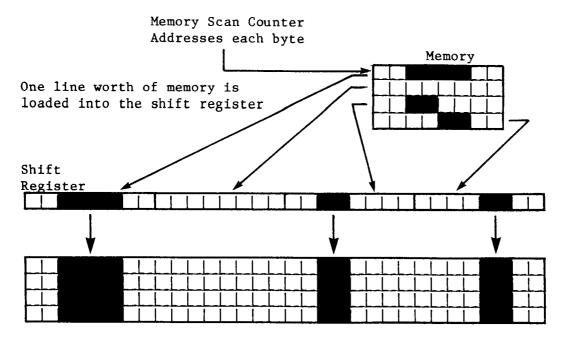

Memory Map Display Instructions: Data in memory (addressed by the Memory Scan Counter) is displayed directly when executing a memory (bit) map display instruction. As data is being displayed it is also stored in a shift register so that it can be redisplayed for as many TV lines as required by the instruction.

Shift register data is displayed for four TV scan lines in this example.

In Instruction Register (IR) display modes 8 through F, one or two bits of memory are used to specify what is to be displayed on each pixel of the screen. Pixel sizes range from 1/2 clock by 1 TV line to 4 clocks by 8 TV lines. The OS and BASIC support most of these graphics modes (BASIC GRAPHICS command). Two modes, C and E, are not supported by the OS. These modes have rectangular pixels, which are approximately twice as wide as they are high.

In IR mode F, only one color (COLPF2) can be displayed. Two different luminances are available. If a bit is a zero, then the luminance of the corresponding pixel comes from COLPF2. If the bit is a one, them the luminance is determined by the contents of COLPF1 (abbreviated to PF1).

In IR modes 9,B, and C, two different colors can be displayed. A zero indicates background color and a one indicates PFO color. The difference between the various modes is in the size of the pixels.

In IR modes 8,A,D, and E, two bits are used to specify the color of each pixel. This allows four different colors to be displayed. However, only four pixels can be packed into each byte, instead of eight as in the previous modes. The bit assignments are shown below.

|                | <br>  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|----------------|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SHIFT REGISTER | <br>6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

2 bits form

one pixel

## Memory Map Display Modes

| OS    |              | Colors       | Pixels       | Bytes        | Scan         | Color                |              | Bit      |        |

|-------|--------------|--------------|--------------|--------------|--------------|----------------------|--------------|----------|--------|

|       | Inst.        | per          | per          | per          | Lines        | Clocks               | Bits         | Values   | Color  |

| BASIC | Reg.         | Mode         | Std.         | Std.         | per          | per                  | per          | in       | Reg.   |

| Modes | HEX          |              | Line         | Line         | Pixel        | Pixel                | Pixel        | Pixel    | Select |

|       |              |              |              |              | 1            | 1                    |              | 00       | BAK    |

| 3     | 8            | 4            | 40           | 10           | 8            | 4                    | 2            | 01       | PFO    |

|       |              |              |              |              |              |                      | 1            | 10       | PF1    |

|       |              |              |              | <u> </u>     | <u></u>      | <u>L</u>             | L            | 11       | PF2    |

|       |              |              | 1            |              | [            |                      | 1            |          |        |

| 4     | 9            | 2            | 80           | 10           | 4            | 2                    | 1            | 0        | BAK    |

|       |              |              | 1            | 1            | 1            |                      | 1            | 1        | PFO    |

|       |              |              | L            |              | L            | <u>L</u>             | <u> </u>     | <u> </u> | LI     |

|       |              |              | 1            |              | 1            |                      |              | 00       | BAK    |

| 5     | A            | 4            | 80           | 20           | 4            | 2                    | 2            | 01       | PFO    |

|       |              |              |              |              |              |                      | -            | 10       | PF1    |

|       | <u> </u>             |              | 11       | PF2    |

|       |              | ]            |              | !            | ļ            | !                    | ļ            | ļ        |        |

| 6     | В            | 2            | 160          | 20           | 2            | 1                    | 1            | 0        | BAK    |

| !     | <u> </u>     | }            | !            | !            | !            | !                    | !            | 1        | PF0    |

| ļ     | <u> </u>     | <u> </u>     | Ļ            | Ļ            | Ļ            | <u> </u>             | Ļ            | <u> </u> | ļ      |

|       |              |              | 1.60         |              | ! .          | [                    | 1            |          |        |

| -     | l c          | 2            | 160          | 20           | 1            | 1                    | 1            | 0        | BAK    |

|       | <br>         | ]            | 1            |              | ļ            |                      |              | 1        | PF0    |

|       | <u> </u>     | <u> </u>     | <del> </del> | <u> </u>     | <del></del>  | <u> </u>             | <u> </u>     | L        | L      |

| 1 7   | l<br>In      | !<br>  4     | <br>  160    | 1 40         | 1            | 1 1                  | 1 2          | 00       | BAK    |

| 1 /   | D .          | 1 4<br>1     | i<br>I TOO   | 40           | 2            | 1                    | 2            | 01       | PF0    |

| 1     | i<br>I       | }<br>1       | ]<br>        | 1            | ]            |                      | 1            | 10       | PF1    |

| ¦     | <del> </del> | <del></del>  | <del> </del> | <del> </del> | <del> </del> | <u> </u>             | <u> </u>     | 11       | PF2    |

| 1     | <br>  F      | <br>  4      | 160          | 1 40         | 1            | <br>  1              | 1            | 00       | BAK    |

| -     | E            | 4<br>        | 1 100        | 40           | 1            | 1                    | 2            | 01       | PF0    |

| ]<br> | !<br>!       | <br>         | <br>         | 1            | <br>         |                      |              | 10       | PF1    |

|       | <del> </del> | <del> </del> | <del> </del> | <u> </u>     | <del> </del> | <del> </del>         | <del> </del> | 11       | PF2    |

| 1 8   | !<br>  F     | 1 1 ½        | 320          | <br>  40     | 1 1          | <br>  1 <sub>2</sub> | 1 1          | 1 0      | 1 000  |

| 1 O   | F            | 1 1.2        | 320<br>      | j 40<br>I    | 1<br>1 T     | <sup>-</sup> 2<br>   | i T          | 0        | PF2    |

| 1     | i<br>1       | 1            | 1            | i<br>i       | 1            | 1                    | l<br>I       | 1        | PF1    |

| I     | L            | <u> </u>     | <del></del>  | L            | L            | <u> </u>             | <u> </u>     | <u> </u> | (LUM)  |

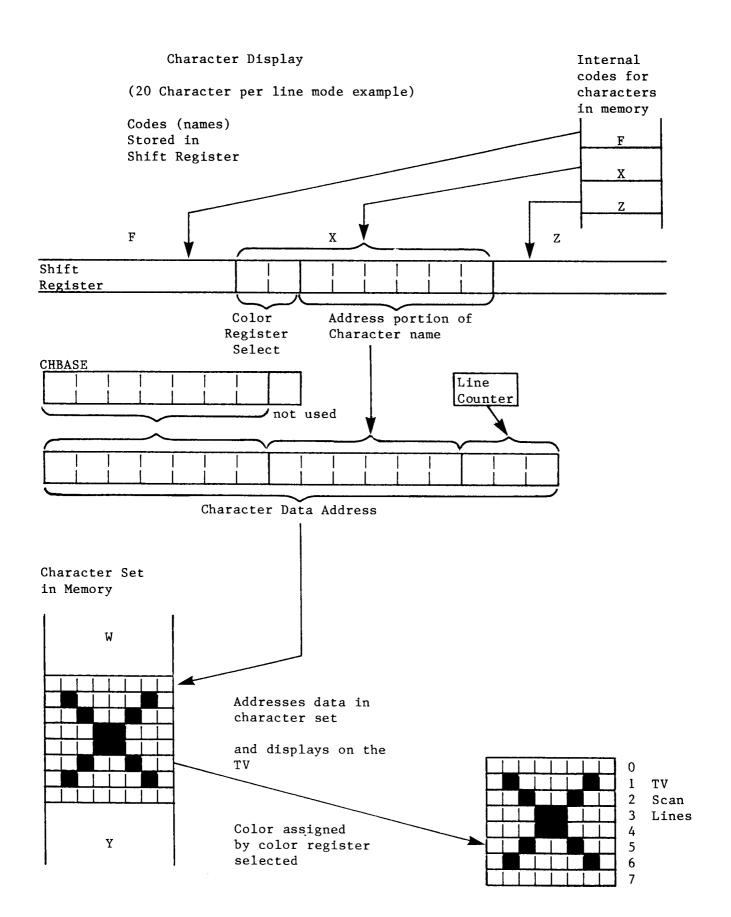

Character Display Instructions: The first step in using the character map mode is to create a character set in memory (or the built-in OS character set at hex E000 may be used). The character set contains eight bytes of data for the graphics for each character. The meaning of the data depends on the mode. The character set can contain 64 or 128 characters, also depending on the mode. The MSB (Most Significant Byte) of the address of the character set is stored in CHBASE (or the OS Shadow CHBAS). Only the most significant six or seven bits of CHBAS are used (see CHBASE description in section III). The other one or two bits and the LSB of the address are assumed to be zero, so the character set must start at an acceptable page boundary.

The next step is to set up the display list for the desired mode. Then the actual display is set up. This consists of a string of character names or codes. Each name takes one byte. The last 6 or 7 bits of the name selects a character. For a 64 character set, the name would range from 0 through 63 (decimal). For a 128 character set, the range would be 0 through 127 (decimal). The upper one or two bits of the name byte are used to specify the color or other special information, depending on the mode.

Character names (codes) are fetched by the memory scan counter, and are placed in a shift register. On any given line of display the shift register rotates, changing only the name portion of the character address, as shown below.

After a full line of character data has been displayed the line counter will increment. The next line again addresses all characters by name for that line number.

In 20 character per line modes the seven most significant bits of CHBASE are used. This requires that the character set to start upon a 512 byte memory boundary. The set must contain 64 characters, 8 bytes each, giving a total of 512 bytes for the set.

The 40 character per line modes use the six most significant bits of CHBASE, forcing the character set to start on a IK byte memory boundary. The set must have 128 characters of 8 bytes each. This gives a total of 1024 bytes for the set.

| Hex<br>Code | Graphics<br>  Mode<br> | Chars.<br>  Per<br>  Line | Number<br>  of<br>  Colors | Bytes<br>  per<br>  Char. | Number<br>  of Char.<br>  in set | Bytes  <br>  in  <br>  Char Set |

|-------------|------------------------|---------------------------|----------------------------|---------------------------|----------------------------------|---------------------------------|

| 1 2         | 1 0                    | 40                        | 2                          | 8                         | 128                              | 1024                            |

| ] 3         | -                      | l<br>  40                 | 2                          | 8                         | 128                              | 1024  <br>  1024                |

| <u> </u> 4  |                        | l 40                      | 4                          | 8                         | 128                              | 1024                            |

| <u> </u>    |                        | <br>  40                  | 4                          | <br>  8                   | 128                              | 1024                            |

| <u> </u> 6  | 1                      | <br>  20                  | 5                          | <br> <br>  8              | 64                               | 512                             |

| 7           | 2                      | 20                        | j<br>5                     | 8                         | 64                               | 512                             |

There are six charcter map modes, IR modes 2 through 7. Modes 2,6 and 7 are supported by the OS and BASIC (GRAPHICS 0,1 and 2).

In IR modes 6 and 7, the upper two bits of each character <u>name</u> select one of four playfield colors. For each <u>data</u> bit that contains a one, the selected playfield color is displayed. For each zero data bit, the background color is displayed. The four character colors plus the background color gives a total of five different colors. the mode 6 characters are eight lines high and the mode 7 characters are sixteen lines high (each data byte is displayed for two lines).

In IR modes 4 and 5, each character is only four pixels wide instead of eight (as in the other modes). Two bits per pixel of data are used to select one of three playfield colors, or background. Seven name bits are used to select the character. If the most significant name bit is a zero then data of 10 (binary) selects PF1. If the name bit 7 is one, then data bits of 10 select PF2. This makes it possible to display two characters with different colors, using the same data but different name bytes.

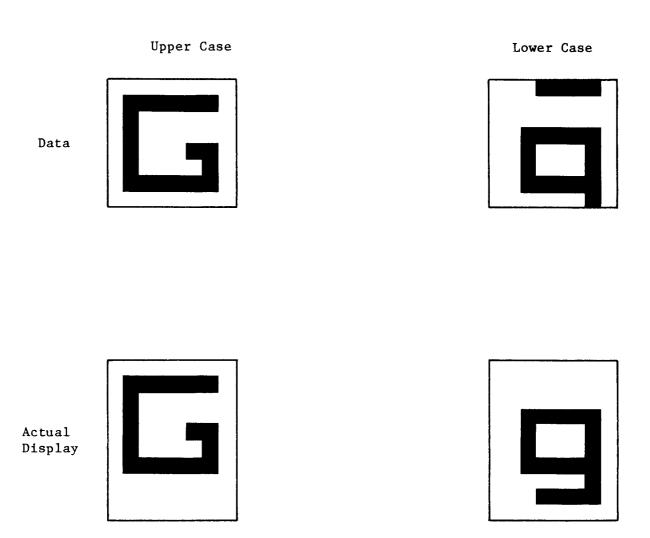

In IR modes 2 and 3, each pixel is half of a color clock in width. This makes it possible to have forty eight-pixel-wide characters in a standard width line. These modes are similar to memory mode F in that two luminances can be displayed, but only one color is available at a time. In IR mode 3, each character is 10 lines high. This makes it possible to define lower case characters with descenders. The last fourth of the character set (name bits 5 and 6 equal to one) is lowered. The hardware takes the first two data bytes and moves them to the bottom of the character, displaying two blank lines at the top of the character (see next page).

In IR modes 2 and 3, bit 7 of the character name is used for inverse video or blanking. This is controlled by CHACTL (Character Control). If bit 2 of CHACTL is a one then all of the characters will be displayed upside down, regardless of mode. If CHACTL bit 1 is set, then each character which has bit 7 of its name set will be displayed in inverse video (the luminances will be reversed). If CHACTL bit 0 is set, then each character which has bit 7 set will be blanked (only background wil be displayed). Characters can be blinked on and off by setting name bit 7 to 1 and toggling CHACTL bit 0. Inverse video and blank apply only to IR modes 2 and 3. If both inverse video and blank are set then the character will appear as an inverse video blank character (solid square).

Hardware Collision Detection: 60 bits of collision register are provided to detect and store overlap (hits) between players, missiles and playfield. These collisions can be read by the microprocessor from addresses D000 through D00F. There are no bits for missile to missile collisions.

- 16 bits for Missile to Playfield

- 16 bits for Player to Playfield

- 16 bits for Missile to Player

- 12 bits for Player to Player (PO to PO always reads as zero, etc.)

The 1/2 clock memory map mode (IR code 1111) and the 1/2 clock Character mode (IR codes 0011 and 0010) are both playfield type 2 collisions and will be stored in bit 2 of the playfield collision registers.

## IR Mode 3-Upper and Lower Case

## Character Map Display Modes

| os       |       |        | Chars. | Scan     | Color    | Data     | Color        | Bit    |          |

|----------|-------|--------|--------|----------|----------|----------|--------------|--------|----------|

| and      | Inst. | Colors | per    | Lines    | Clocks   | Bits     | Select       | Values | Color    |

| BASIC    | Reg.  | per    | Std.   | per      | per      | per      | Bits In      | in     | Reg.     |

| Modes    | HEX   | Mode   | Line   | Char.    | Pixel    | Pixel    | Name         | Data   | Select   |

|          |       |        |        |          |          |          |              |        |          |

| 0        | 2     | 1 1 2  | 40     | 8        | 1/2      | 1        | _            | 0      | PF2      |

|          |       |        |        |          |          |          |              | 1      | PF1      |

| I        |       | L      |        | L        | L        | L        |              |        | (LUM)    |

|          |       |        |        |          |          |          |              |        |          |

| -        | 3     | 1 ½    | 40     | 10       | 1 2      | 1        | i <b>-</b>   | 0      | PF2      |

| 1        |       |        |        |          |          |          |              | 1      | PF1      |

| l        |       |        |        |          |          |          |              | L      | (LUM)    |

|          |       |        |        |          |          |          |              | 00     | BAK      |

| -        | 4     | 5      | 40     | 8        | 1        | 2        | Bit 7        | 01     | PFO      |

| 1        |       |        |        | İ        |          |          | = 0          | 10     | PF1      |

|          |       |        |        | ,        |          |          |              | 11     | PF2      |

|          |       |        |        |          |          | 1        |              |        |          |

| ! !      |       |        |        | l        |          |          | Bit 7        | 11     | PF3      |

| <u> </u> |       |        |        | <u> </u> |          | <u> </u> | = 1          |        |          |

|          |       |        |        |          |          | ]        |              | 00     | BAK      |

| -        | 5     | 5      | 40     | 16       | 1        | 2        | Bit 7        | 01     | PFO      |

|          |       |        |        |          |          | ļ        | = 0          | 10     | PF1      |

|          |       |        |        |          |          | !        |              | 11     | PF2      |

|          |       |        |        |          |          | <u> </u> |              |        |          |

| !        |       |        |        | !        |          | }        | Bit 7        | 11     | PF3      |

|          |       |        |        |          | <u> </u> | L        | = 1          |        | <u> </u> |

|          |       | _      | 0.0    |          |          | ! .      | _            | 0      | BAK      |

| 1 1      | 6     | 5      | 20     | 8        | 1        | 1        | 00           | 1      | PFO      |

|          |       |        |        | <u> </u> | Ì        | 1        | 01           | 1      | PF1      |

|          |       |        |        |          |          | 1        | 10           | 1      | PF2      |

|          |       |        |        | L        |          |          | 11           | 1      | PF3      |

|          | -     |        |        |          | ,        | i<br>    | <del>-</del> | 0      | BAK      |

| 2        | 7     | 5      | 20     | 16       | 1        | 1        | 00           | 1      | PFO      |

|          |       |        | 1      | <br> -   | 1        | ļ        | 01           | 1      | PF1      |

|          |       |        |        | [<br>'   | l<br>•   | <br> -   | 10           | 1      | PF2      |

| I        |       |        |        | L        |          | L        | 11           | 11     | PF3      |

Vertical and Horizontal Fine Scrolling: Playfield objects are difficult to move smoothly. Memory map playfield can be moved by rewriting sections of memory. However, this is extremely time-consuming if large sections of the screen must be moved smoothly. Character playfield objects can be moved easily in a jerky fashion by changing the memory scan counter. However, this results in a large position jump from one character position to another, not a smooth motion. For this reason hardware registers (VSCROL and HSCROL) and counters are provided to allow smooth horizontal or vertical motion, up to one character width horizontally and up to one character height vertically. After this much smooth motion has been done by increasing the value in these registers, memory is rewritten or the memory scan counter is modified and smooth motion is resumed for another character distance.

Vertical Scrolling: A zone of playfield on the screen can be scrolled upward by using VSCROL and bit 5 of the display list instruction. The display blocks at the upper and lower boundaries of the zone must have a variable vertical size. In particular, the first display block within that zone must be shortened from the top, and the last display block must be shortened from the bottom (i.e. not all of the top and bottom blocks will be displayed).

The vertical dimension of each display block is controlled by a 4 bit counter within the ANTIC, called the 'Delta Counter' (DCTR). Without vertical scrolling, it starts at 0 on the first line, and counts up to a standard value, determined by the current display instruction. (Ex: for upper and lower case text display, the end value is 9. For 5 color character displays, it is 7 or 15.)

If bit 5 of the instruction remains unchanged between consecutive display blocks, then the second block is displayed in the normal fashion. If bit 5 of the instruction goes from 1 to 0 between two consecutive display blocks, the second block will start with Delta = 0, as usual, but will count up until delta=VSCROL, instead of the standard value. This shortens that display block from the bottom.

To define a vertically scrolled zone, the most direct method is to set bit 5 to 1 in the first display instruction for that zone, and in all consecutive blocks but the last one. If the VSCROL register is not rewrittren on the fly, this results in a total scrolled zone that has a constant number of lines (provided that the VSCROL value does not exceed the standard individual block size). If N is the standard block size, the top block will be N-VSCROL lines (N > VSCROL ), and the last block will be VSCROL + 1 lines: (N-VSCROL) + (VSCROL + 1) = N + 1. Shown on the following page is an example of a scrolled zone, top block, for 8 VSCROL values for N = 8.

Horizontal scrolling is described under HSCROL in section III.

| bit 5 =Ø VSCROL=Ø | VSCROL=1 | VSCROL=2                | VSCROL=3                                                      | VSCROL=4                                                 | VSCROL=5                                            | VSCROL=6                                       | VSCROL=7                                  |

|-------------------|----------|-------------------------|---------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|------------------------------------------------|-------------------------------------------|

| bit 5 = Ø         | 0        | 2 3 4 5 6 7 0 1 2 3 4 5 | 3<br>4<br>5<br>6<br>7<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 4<br>5<br>6<br>7<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 5<br>6<br>7<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 6<br>7<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 7<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 |

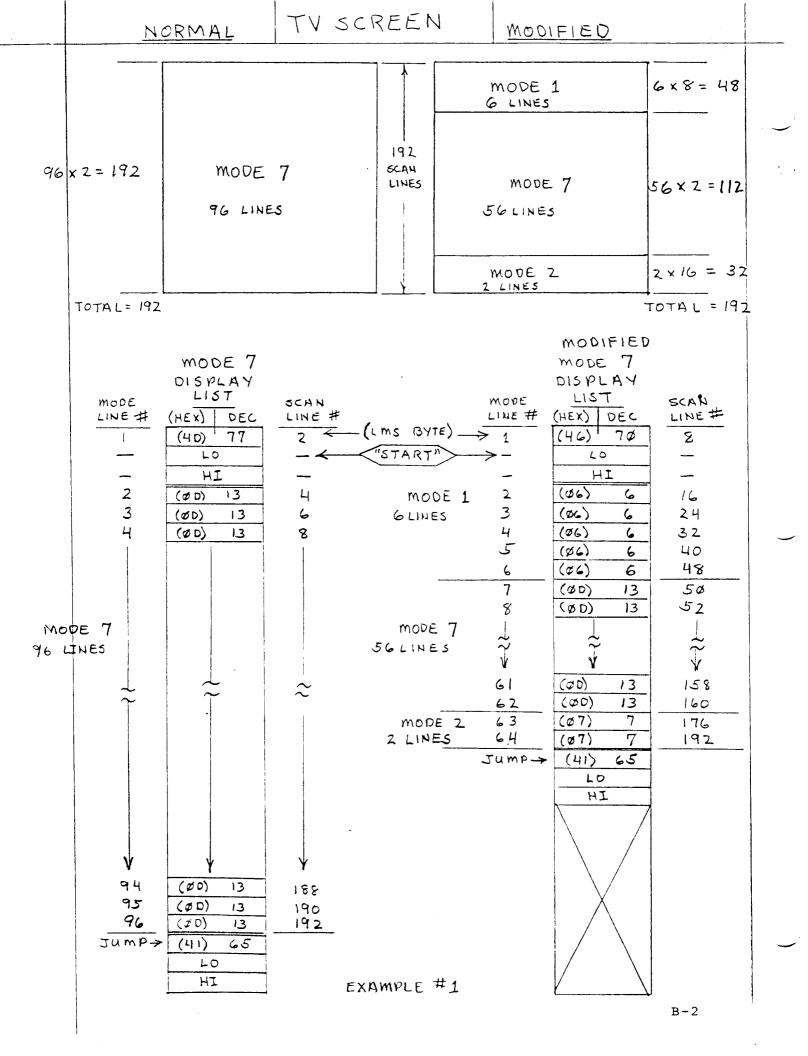

Simple Display List Example: BASIC starts out in OS graphics mode 0 which displays 40 characters across by 24 rows. This is IR mode 2 with a standard screen width. The OS sets up the display list near the top of RAM with room for the character names at the top of RAM. On a 32 K-byte machine, the display list would start at hex 7C20. The next three bytes are hex 70's to create 24 blank lines. The next byte is a hex 42. 4 tells the hardware to reload the memory scan counter with the following address (7C40). This is the address of the data to be displayed. tells the hardware to display one line of IR mode 2 characters. The next 23 bytes specify 23 more lines of mode 2 characters. Hex 41 is the code for jumping and waiting until the end of the next vertical blank. The address to jump to is 7C20, the start of the display list. The next 960 bytes are the list of characters to be displayed, 40 bytes per line. The OS must set up the display list pointer (DLISTH and DLISTL) to the starting address of the display list (7C20). It also sets CHBASE to the MSB of the address of the character set (E0).

This is a simple example because only one mode is used and the memory scan counter is only loaded at one point. It is possible to have different modes on different lines, change character sets and colors, etc., as shown in the example in Section IV.

### OS Mode O Display List (40 chars x 24 lines)

| Address (hex) | Data (hex)                                                         |

|---------------|--------------------------------------------------------------------|

| 7C20          | 70 70 70 70 42 70 1R mode 2                                        |

| ·             | 2 2 2 2 3 2 3 23 more IR mode 2 instructions 2 2 2                 |

|               | 2 J 41 Jump back to 7C20 and 20 wait for end of vertical blank. 7C |

| 7C40          | 960 bytes of display data (character names)                        |

Cycle Counting: As explained previously, the ATARI 800 6502 microprocessor runs at a rate of 114 machine cycles per TV line (1.79 MHZ). There are 262 lines per TV frame and 60 frames per second on the NTSC (US) system. (The PAL (Europeon) system is different. See the section on NTSC vs. PAL.)

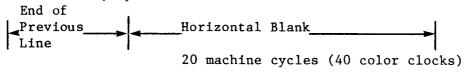

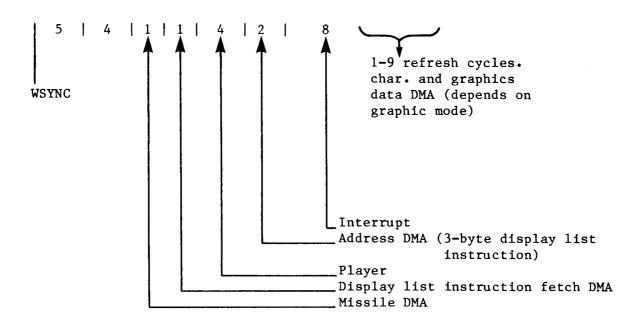

Each machine cycle is equivalent in length to 2 color clocks. There are 228 color clocks on a TV line. The highest resolution graphics modes have a pixel size of 1/2 color clock by 1 TV line. Horizontal blank takes 40 machine cycles. This is when the beam returns to the left edge of the screen in preparation for displaying the next TV line. A wait for Sync (WSYNC) instruction stops the 6502. The processor is restarted exactly 7 machine cycles before the beginning of the next TV line. The program can thus change graphics or colors during horizontal blank in preparation for the next line.

The ANTIC chip steals cycles from the 6502 in order to do memory refresh and fetch graphics data when needed. The general rule to remember is that each byte fetched from memory requires one machine cycle. If a display list memory map instruction extends over several lines then the data is only fetched on the first line. Memory refresh takes 9 cycles out of every line, unless pre-empted by a high-resolution graphics mode. Memory refresh continues during vertical blank.

Missile DMA takes one cycle per line in the one-line resolution mode and one cycle every other line in the two line resolution mode. Missile DMA can be enabled without doing player DMA. However, if player DMA is enabled then missile DMA will also be done (see DMACTL, GRACTL bits). Player DMA requires 4 cycles every one or two lines, depending on the resolution used.

Each fetch of a display list byte takes one cycle, so three cycles are required for a three byte instruction.

Player/missile and display list instruction fetch DMA take place during horizontal blank, if they are required for the next line.

In memory map modes, the graphics data is fetched as needed throughout the first line of the display list instruction, then saved by ANTIC for use in succeeding lines. In character modes, the character codes are fetched during the first line of each row of characters, along with the graphics data needed for that line. On the next lines, only the graphics data is fetched, since ANTIC remembers the character codes.

In the 40 x 24 character mode, with a standard screen width, most of the cycles during the top line of each row of characters are requried to fetch the character codes and data, so there is only time for one memory refresh cycle instead of the usual nine. Less DMA is required with a narrow screen width so two memory refresh cycles would occur in this case.

The memory refresh is done fast enough to make up for the lost cycles in the high resolution modes. Once memory refresh starts on a line, it occurs every four cycles unless pre-empted by DMA.

All interrupts reach the 6502 near the end of horizontal blank. With standard or narrow screen widths, refresh DMA starts after the end of horizontal blank.

The time at which ANTIC does cycle stealing is deterministic, but depends on the graphics mode, screen width and whether or not horizontal scrolling is enabled. Horizontal scrolling requires extra graphics data: see HSCROL.

ANTIC does horizontal scrolling of an even number of color clocks by delaying the time at which it DMA's the data. To do an odd number of color clocks (which involves half of a machine cycle), ANTIC has a one color clock internal delay.

Theoretically, it is possible to write a program which changes graphics or colors "on the fly", i.e. during the middle of a TV line. However, with all the DMA going on, the cycle counting gets to be quite complicated, and is beyond the scope of this manual.

There are a number of delays associated with the display of graphics. These occur in the ANTIC and the CTIA. The ANTIC sends data to the CITA which adds in the color information. Thus the timing for changing colors on the fly is different from that for changing graphics on the fly.

## Horizontal Blank DMA Timing

When DMA is enabled, cycles are stolen at the times shown below.

Cycle Counting Example: This example uses the 40 character by 24 line display list given on page II.24. This display list is 32 bytes long so display list DMA takes 32 machine cycles. It takes 960 cycles to DMA the characters and 8\*960 to DMA the character data. The refresh DMA takes 9 cycles for each of 262 lines, except for the 24 lines where the characters are read, where only 1 refresh cycle occurs.

| DMA description | Machine    | cycles |

|-----------------|------------|--------|

| display list    |            | 32     |

| characters      | 40x24      | = 960  |

| character data  | 960x8      | =7680  |

| refresh         | 262x9-24x8 | =2166  |

| total           |            | 10838  |

Thus the total DMA per frame is 10838 machine cycles. One frame is 262 lines with 114 machine cycles per line for a total of 29868 machine cycles per frame. Thus 36% of each frame is required for DMA in OS graphics mode 0.

NTSC vs. PAL Systems: There are two versions of the ATARI 800: the NTSC (United States T.V. standard) and PAL (one of the European T.V. standards). The PAL system has been designed so that most programs will run without being modified. However, some differences may be noticeable. There is a hardware register (PAL) which a program can read to determine which type of system it is running on and adjust accordingly.

The PAL T.V. has a slower frame rate (50 Hz. instead of 60 Hz.) so games will be slower unless an adjustment is made. PAL has more T.V. lines per frame (312 instead of 262). The Atari 800 hardware compensates for this by adding extra lines at the beginning of vertical blank. Display lists do not have to be altered. However, their actual vertical height will be shorter. PAL ATARI 800 colors are similar to NTSC because of a hardware modification.

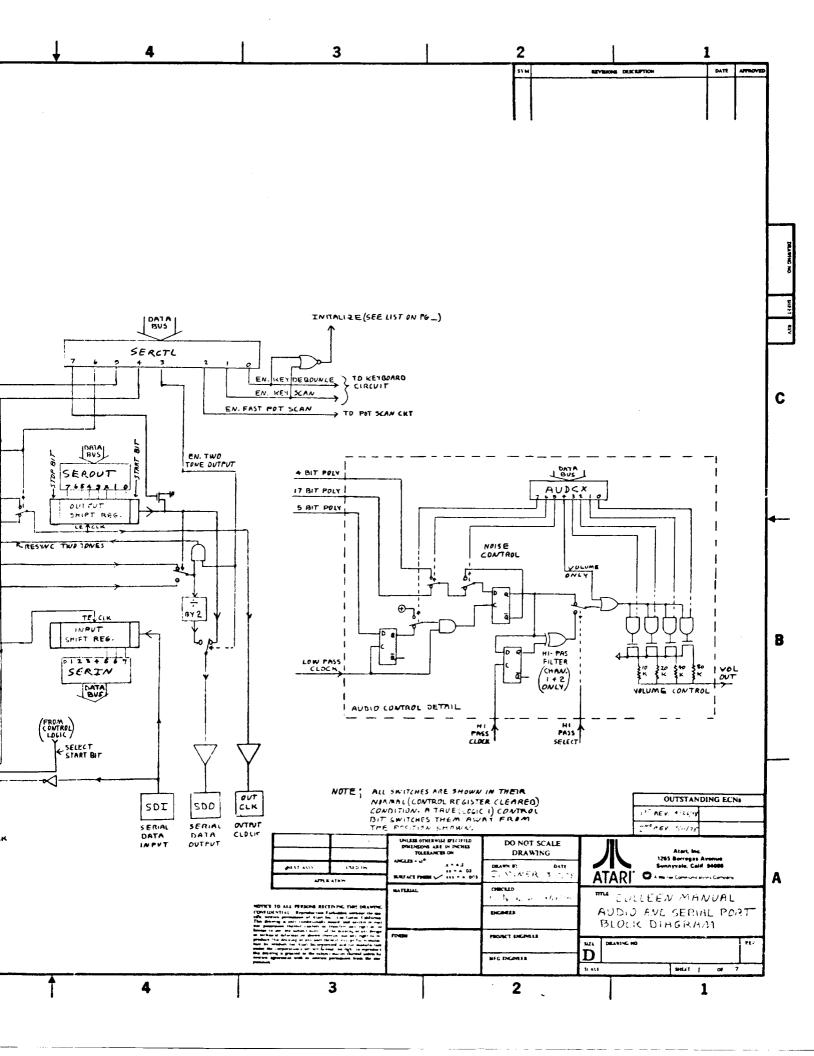

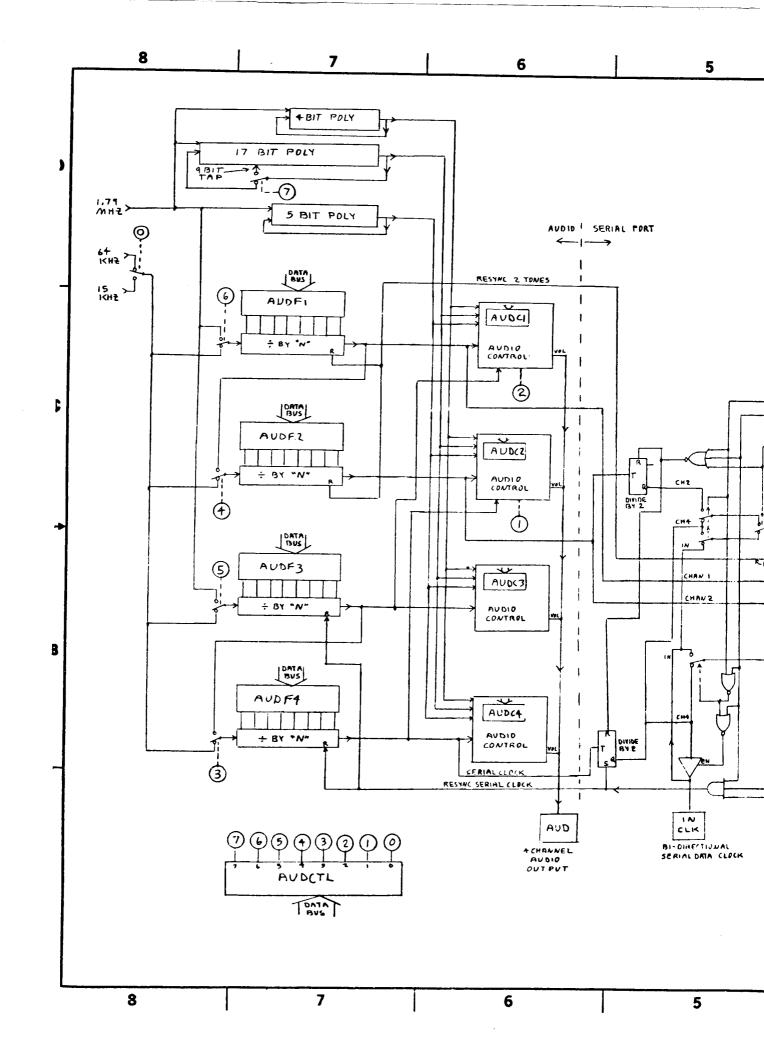

#### B. POKEY

Audio: There are 4 semi-independent audio channels, each with its own frequency, noise, and volume control. Each has an 8 bit "divide by N" frequency divider, controlled by an 8 bit register (AUDFX). (See audio-serial port block diagram.) Each channel also has an 8 bit control register (AUDCX) which selects the noise (poly counter) content, and the volume.

Frequency Dividers: All 4 frequency dividers can be clocked simultaneously from 64 KHZ or 15 KHZ. (AUDCTL bit 0). Frequency dividers 1 and 3 can alternately be clocked from 1.79 MHZ (AUDCTL bits 6 and 5). Dividers 2 and 4 can alternately be clocked with the output of dividers 1 and 3 (AUDCTL bits 4 and 3). This allows the following options: 4 channels of 8 bits resolution, 2 channels of 16 bit resolution, or 1 channel of 16 bit and 2 channels of 8 bit.

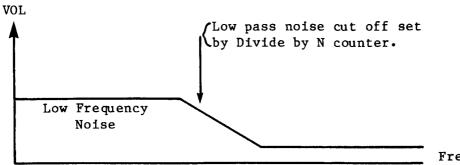

Poly Noise Counters: There are 3 polynomial counters (17 bit, 5 bit and 4 bit) used to generate random noise. The 17 bit poly counter can be reduced to 9 bits (AUDCTL bit 7). These counters are all clocked by 1.79 MHZ. Their outputs, however, can be sampled independently by the four audio channels at a rate determined by each channel's frequency divider. Thus each channel appears to contain separate poly counters (3 types) clocked at its own frequency. This poly counter noise sampling is controlled by bits 5,6 and 7 of each AUDCX register. Because the poly counters are sampled by the "divide by N" frequency divider, the output obviously cannot change faster than the sampling rate. In these modes (poly noise outputted) the dividers are therefore acting as "low pass" filter clocks, allowing only the low frequency noise to pass.

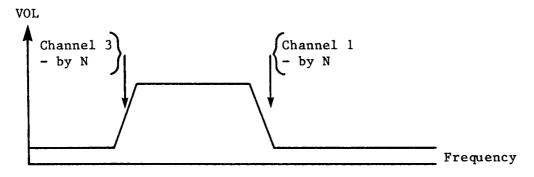

The output of the noise control circuit described above consists of pure tones (square wave type), or polynomial counter noise at a maximum frequency set by the "divide by N" counter (low pass clock). This output can be routed through a high pass filter if desired (AUDCTL bits 1 and 2).

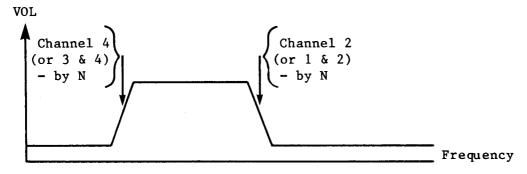

## Audio Noise Filters:

Frequency

Any channel noise output (without high pass filter)

Channel l output (with high pass filter)

Channel 2 output (with high pass filter)

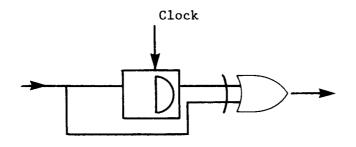

High Pass Filters: The high pass filter consists of a "D" flip flop and an exclusive-OR Gate. The noise control circuit output is sampled by this flip flop at a rate set by the "High Pass" clock. The input and output of the Flip Flop pass through the exclusive-OR Gate. If the flip flop input is changing much faster than the clock rate, the signal will pass easily through the exclusive-OR Gate. However, if it is lower than the clock rate, the flip flop output will tend to follow the input and the two exclusive-OR Gate inputs will mostly be identical (11 or 00) giving very little output. This gives the effect of a crude high pass filter, passing noise whose minimum frequency is set by the high pass clock rate. Only channels 1 and 2 have such a high pass filter. The high pass clock for channel 1 comes from the channel 3 divider. The high pass clock for channel 2 comes from the channel 4 divider. This filter is included only if bit 1 or 2 of AUDCTL is true.

Volume Control: A volume control circuit is placed at the output of each channel. This is a crude 4 bit digital to analog converter that allows selection of one of 16 possible output current levels for a logic true audio input. A logic zero audio input to this volume circuit always gives an open circuit (zero current) output. The volume selection is controlled by bits 0 thru 3 of AUDCX. "Volume Control only" mode can be invoked by forcing this circuit's audio input true with bit 4 of AUDCX. In this mode the dividers, noise counters, and filter circuits are all disconnected from the channel output. Only the volume control bits (0 to 8 of AUDCX) determine the channel output current.

The audio output of any channel can be completely turned off by writing zero to the volume control bits of AUDCX. All ones gives maximum volume.

#### C. SERIAL PORT

The serial port consists of a serial data output (transmission) line, a serial data input (receiver) line, a serial output clock line, a bi-directional serial data clock line, and other miscellaneous control lines described in the Operating System Manual. Data is transmitted and received as 8 bits of serial data preceded by a logic zero start bit, and succeeded by a logic true stop bit. Input and output clocks are equal to the baud (bit) rate, not 16 times baud rate. Transmitted data changes when the output clock goes true. Received data is sampled when the input clock goes to zero.

Serial Output: The transmission sequence begins when the processor writes 8 bits of parallel data into the serial output register (SEROUT)(see audio and serial port block diagram). When any previous data byte transmission is finished the hardware will automatically transfer new data from (SEROUT) to the output shift register, interrupt the processor to indicate an empty (SEROUT) register (ready to be reloaded with the next byte of data), and automatically serially transmit the shift register contents with start—stop bits attached. If the processor responds to the interrupt, and reloads SEROUT before the shift register is completely transmitted, the serial transmission will be smooth and continuous.

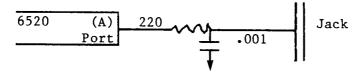

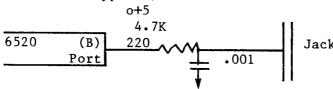

Output data is normally transmitted as logic levels (+4V=true OV=False). Data can also be transmitted as two tone information. This mode is selected by bit 3 of SKCTL. In this mode audio channel 1 is transmitted in place of logic true, and audio channel 2 in place of logic zero. Channel 2 must be the lower tone of the tone pair.

The processor can force the data output line to zero (or to audio channel 2, if in two tone mode) by setting bit 7 of SKCTL. This is required to force a break (10 zeros) code transmission.

Serial Output Clock: The serial output data always changes when the serial output clock goes true. The clock then returns to zero in the center of the output data bit time.

The baud (bit) rate of the data and clock is determined by audio channel 4 audio channel 2, or by the input clock, depending on the serial mode selected by bits 4, 5, and 6 of SKCTL. (See chart at end of this section.)

Serial Input: The receiving sequence begins when the hardware has received a complete 8 bit serial data word plus start and stop bits. This data is automatically transferred to the 8 bit parallel input register (SERIN), and the processor is interrupted to indicate an input data byte ready to read in SERIN. The processor must respond to this interrupt, and read SERIN, before the next input data word reception is complete, otherwise an input data "over-run" will occur. This over-run will be indicated by bit 5 of SKSTAT (if bit 5 of IRQST is not RESET (true) before next input complete), and means input data has been lost. This bit should be tested whenever SERIN is read. Bit 7 of SKSTAT should also be tested to detect frame errors caused by extra (or missing) data bits.

<u>Direct Serial Input</u>: The serial data input line can be read directly by the microprocessor if desired, ignoring the shift register, by reading bit 4 of SKSTAT.

<u>Bi-Directional Clock</u>: This clock line is used to either receive a clock from an external clock source for clocking transmitted or received data, or is used to supply a clock to external devices indicating the transmit or reception rate. This clock line direction is determined by the serial mode selected by bits 4, 5, and 6 of SKCTL. (See mode chart at the end of this section.) Transmitted data changes on the rising edge of this clock. Received data is sampled on the trailing edge of this clock.

Asynchronous Serial Input: Unclocked serial data (at an approximately known (+5%) rate) can be received in the asynchronous modes. The receive (input) shift register is clocked by audio channel 4. Channels 3 and 4 should be used together (AUDCTL bit 3 = 1) for increased resolution. In asynchronous modes, channels 3 and 4 are reset by each start bit at the beginning of each serial data byte. This allows the serial data rate to be slightly different from the rate set by channels 3 and 4.

<u>Serial Mode Control</u>: There are 6 useful modes (of the possible 8) controlled by bits 4, 5, and 6 of SKCTL. These are described on the next page.

Note that two tone output (bit 3 of SKCTL) may be used in any of these modes except for the bottom pair. This is because channel 2 is used to set the output transmit rate and is therefore not available for one of the two tones.

Note that the output clock rate is identical to the output data rate.

## Serial Mode Control (see also register description SKCTL):

Force Break

| D7 | D6       | D5                                               | D4       | D3 D2        | D1 D0     | SK            | CTL REGIST   | ГER                                                            |

|----|----------|--------------------------------------------------|----------|--------------|-----------|---------------|--------------|----------------------------------------------------------------|

|    |          |                                                  |          |              |           | Po            | t scan and   | d keyboard CTRL                                                |

|    |          | <br>                                             |          | <br>         | Two Ton   | ie Contr      | ·01          |                                                                |

|    |          |                                                  |          | İ            |           |               |              |                                                                |

|    |          | <br>                                             |          | <u>М</u> с   | de Contr  | ol Bits       | 3            | A=asynchronous                                                 |

|    |          |                                                  |          | !<br>L       |           |               |              |                                                                |

| _  |          |                                                  | <u></u>  | Out          | Out       |               |              |                                                                |

| _  | υ6       | <u>D5</u>                                        | D4       | Rate         | Clock     | Rate          | Clock        | Comments                                                       |

|    | 0        | 1<br>10                                          | I<br>  0 | l l<br>ext   | ext       | ext 1         | ext<br>input | Trans. & Receive rates set by   external clock. Also internal  |

| _  | Ĺ        | L                                                | Ĺ        |              |           |               |              | clock phase reset to zero.                                     |

|    |          | <u> </u>                                         | <u> </u> |              |           |               |              |                                                                |

|    |          |                                                  |          |              |           | chan          | ext          | Trans. rate set by external                                    |

|    | U<br>    | U<br>                                            | l I      | ext          | ext       | 4  <br>A      | input        | clock. Receive asynch. (ch. 4)  <br>(CH3 and CH4)              |

| -  | L<br>    | <u> </u>                                         | <br>     | <del> </del> |           | A             |              |                                                                |

| -  |          | <del>                                     </del> | l        | 1            |           |               | chan         | Trans. & Receive rates set by                                  |

|    | 0        | 1                                                | 0        | chan         | chan      | chan          | 4            | Chan. 4. Chan. 4 output on Bi-                                 |

| _  | <u> </u> | <u></u>                                          | Ļ        | 4            | 4         | 4             | output       | Directional clock line.                                        |

| -  | 0        | 1                                                | 1        | CH4          | CH4       | CH4           |              |                                                                |

|    |          | -                                                |          | A            | A         | A             | input        |                                                                |

| _  |          |                                                  |          |              |           |               |              |                                                                |

|    |          |                                                  |          | chan         |           | ext           | ext          | Trans. Rate Set by Chan. 4                                     |

|    | 1        | 0                                                | 0        | 4            | 4         |               | input        | Receive Rate set by External                                   |

| -  | <u> </u> | <del></del>                                      |          | <u> </u>     |           |               |              | Clock.                                                         |

| -  | 1        | 0                                                | 1        | CH4          | CH4       | CH4           |              | Not Useful                                                     |

| -  | <u> </u> | <u> </u>                                         | <u> </u> | A            | A         | A             | input        |                                                                |

| -  | <u> </u> | <u> </u>                                         | <u> </u> | I Ch and     | Ch        |               |              |                                                                |

|    | <br>  1  | 1                                                | 1<br>  0 | Chan <br>  2 | Chan<br>2 | Chan  <br>  2 | Chan<br>4    | Trans. rate set by chan. 2   Recieve rate set by chan. 4 Chan. |

|    | Ĺ        | Ĺ                                                | Ĺ        |              |           |               | Output       | 4 out on Bi-Direct. Clock line.                                |

| -  |          |                                                  |          |              |           |               |              |                                                                |

|    |          |                                                  |          |              |           |               | Input        | Trans. Rate set by Chan. 2. Re-                                |

|    | 1        | 1                                                | 1        | Chan         | •         | Chan          | not          | ceive async. (chan 3&4) Bi-Dir.                                |

|    | <br>     | <br>                                             | 1        | 2<br>        | 2         | 4<br>  A      | l used       | Clock not used (Tri-state condi-   tion)                       |

| -  | <u> </u> | Ь                                                | ┺        | L            | L         | A             | L            | [[10]]                                                         |

Two tone (bit3) not useable in these modes

### D. INTERRUPT SYSTEM

There are two basic types of interrupts defined on the microprocessor: NMI (non maskable interrupt) and IRQ (interrupt request). It is recommended that a thorough understanding of these interrupt types be acquired by reading all chapters concerning interrupts in the 6502 microprocessor programming and hardware manuals.

In this system NMI interrupts are used for video display and reset. IRQ interrupts are used for serial port communication, peripheral devices, timers, and keyboard inputs.

NMI Interrupts: Even though NMI interrupts are "unmaskable" on the micrprocessor, this system has interrupt enable (mask) bits for NMI function. (Bits 6 and 7 of NMIEN) When these bits are zero NMI interrupts are disabled (masked) and prevented from causing a microprocessor NMI interrupt. (see NMIEN register description) The 3 types of NMI interrupts are:

- 1. D7 = Instruction Interrupt (during display time any display

instruction with bit 7=1 will cause this interrupt to occur

(if enabled) at the start of the last video line displayed by

that instruction.)

- 2. D6 = Vertical Blank Interrupt (interrupt occurs (if enabled) at the beginning of the vertical blank time interval.)

- 3. D5 = Reset Button Interrupt (pushing the SYSTEM RESET button will cause this interrupt to occur.)

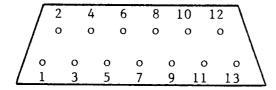

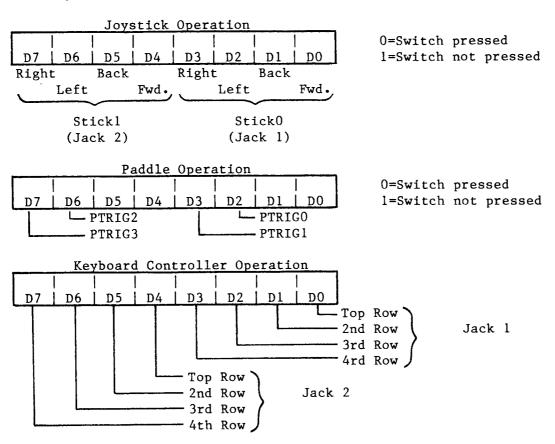

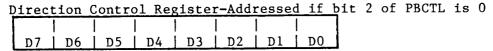

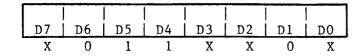

Since any of these interrupts will cause the processor to jump to the same NMI address, the system also has NMI status bits which may be examined by the processor to determine which source caused the NMI interrupt. Bits 5, 6, and 7 of NMIST serve this function (see NMIST register description). These status bits are set by the corresponding interrupt function (even if the interrupt is masked from the processor by NMIEN). The status bits may be reset together by writing to the address NMIRES.