•

# ASSEMBLY LANGUAGE PROGRAMMING FOR THE 68000 FAMILY

18-55

Related Titles of Interest from John Wiley & Sons

PROGRAMMING WITH MACINTOSH PASCAL, Swan EXCEL: A POWER USER'S GUIDE, Hodgkins JAZZ AT WORK, Venit & Burns MACINTOSH LOGO, Haigh & Radford DESKTOP PUBLISHING WITH PAGEMAKER FOR THE MACINTOSH, Bove & Rhodes SCIENTIFIC PROGRAMMING WITH MAC PASCAL, Crandall

# ASSEMBLY LANGUAGE PROGRAMMING FOR THE 68000 FAMILY

Thomas P. Skinner

John Wiley & Sons, Inc. New York • Chichester • Brisbane • Toronto • Singapore Intel is a trademark of Intel Corporation. Amiga is a trademark of Commodore International. Apple and Macintosh are trademarks of Apple Computer, Inc. Atari and Atari ST are trademarks of Atari Corp. IBM and IBM PC are trademarks of International Business Machines, Inc. Motorola is a trademark of Motorola, Inc. Radio Shack and Color Computer are trademarks of Radio Shack.

Publisher: Stephen Kippur Editor: Therese A. Zak Managing Editor: Ruth Greif Editing, Design, and Production: Publishing Synthesis, Ltd. Composition: McFarland Graphics

This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold with the understanding that the publisher is not engaged in rendering legal, accounting, or other professional service. If legal advice or other expert assistance is required, the services of a competent professional person should be sought. FROM A DECLARATION OF PRINCIPLES JOINTLY ADOPTED BY A COMMITTEE OF THE AMERICAN BAR ASSOCIATION AND A COMMITTEE OF PUBLISHERS.

Copyright © 1988 by John Wiley & Sons, Inc.

All rights reserved. Published simultaneously in Canada.

Reproduction or translation of any part of this work beyond that permitted by section 107 or 108 of the 1976 United States Copyright Act without the permission of the copyright owner is unlawful. Requests for permission or further information should be addressed to the Permission Department, John Wiley & Sons, Inc.

Library of Congress Cataloging-in-Publication Data

Skinner, Thomas P. Assembly language programming for the 68000 family/Thomas P. Skinner. p. cm. ISBN 0-471-85357-7 1. Motorola 68000 series microprocessors—Programming. 2.Assembler language (Computer program language) I. Title: QA76.8.M695558 1988 005.265—dc19 CIP

Printed in the United States of America

88 89 10 9 8 7 6 5 4 3 2 1

To my wife Linda

ŗ

5

### PREFACE

This book deals specifically with the Motorola 68000 family of microprocessors. It is primarily about assembly language programming. Chances are that a reader interested in assembly language programming is familiar with computers and their programming; In the unlikely event that you are not, and have picked up this book expecting to learn all about computers, I want to urge you to start elsewhere. In order to gain the maximum knowledge from this book, you should already be familiar with computers in general and have written some programs in a high-level language such as BASIC or Pascal. It is not necessary to know another assembly language or be an expert in computer programming. I start at a fairly low level but get up to speed pretty quickly. Those who already know another assembly language will be able to progress rapidly through the material. In the writing of this book I attempted to strike a balance between a beginner-level tutorial and the brief format of a reference manual. This level of presentation should appeal to the majority of readers.

There are 15 chapters plus a number of useful appendices. Chapter 1 covers number systems. This is mostly general information, but there is a little bit of 68000-specific information here. You should look through it even if you know number systems inside out. Chapter 2 describes microcomputer architectures in general, and the 68000 specifically.

Chapters 3 through 5 provide enough information to start writing complete programs. Chapters 6 through 8 cover more advanced topics such as addressing modes and subroutines. Once through chapter 8 you will have a substantial background in 68000 assembly language. At this point Chapter 9 presents a major program, a linked list manager. This helps to cement the techniques from Chapters 1 through 8.

Chapters 10 through 12 cover advanced topics such as exception handling, shift and rotate instructions, and advanced arithmetic. By the end of Chapter 12 you will know all the instructions of the 68000. Chapters 13, 14, and 15 cover the newest members of the 68000 family—the 68010, 68020, and 68030. Chapter 15 should be of special interest, since it provides an introduction to the latest and most powerful 68000 processor. You will be hearing more about the 68030 as it is introduced into systems. It is destined to have a major impact on the computer systems of the next decade. Of special note is Appendix B, which provides program shells. These shells allow you to start programming with the Atari ST, the Apple Macintosh, or the Commadore Amiga. Without these program shells it would require a good deal of effort just to learn how to interface to your operating system.

A number of people provided assistance along the way. Among my students who helped out were Carol Cook and An-Ping Chi. Special thanks to Mike Mellone and John Saywell, who helped prepare the appendices. Finally, I would like to thank Motorola for their cooperation and permission to reprint information from their 68000 manuals.

Thomas P. Skinner

## CONTENTS

| INTRODUCTION |                                      | .1 |

|--------------|--------------------------------------|----|

| CHAPTER 1:   | Number Systems                       | 5  |

|              | Decimal                              | 5  |

|              | Binary                               | 6  |

|              | Conversions                          | 6  |

|              | Hexadecimal                          | 8  |

|              | Arithmetic in Binary and Hexadecimal | 9  |

|              | Bits, Bytes, Words and Longwords     | 10 |

|              | Representing Negative Values         | 11 |

|              | ASCII Character Codes                | 12 |

|              | Exercises                            | 13 |

|              | Answers                              | 14 |

| CHAPTER 2:   | Microcomputer Architecture           | 17 |

|              | The Motorola M68000 Family           | 17 |

|              | The CPU                              | 20 |

|              | Memory                               | 21 |

|              | User and Supervisor Modes            | 23 |

|              | The CPU Registers                    | 24 |

|              | Input/Output                         | 26 |

|              | Exercises                            | 26 |

|              | Answers                              | 27 |

| CHAPTER 3:   | Assembler Source Format              | 29 |

|              | The Label Field                      | 30 |

|              | The Operation Field                  | 31 |

|              | The Operand Field                    | 31 |

|              | The Comment Field                    | 33 |

|              | On Choosing Symbols                  | 34 |

|              | Constants                            | 34 |

|              | Data-Defining Directives             | 36 |

|              | Symbol Equates                       | 37 |

|              | The END Directive                    | 38 |

|              | Exercises                            | 38 |

|              | Answers                              | 39 |

| CHAPTER 4: | Getting Started                              | 41  |

|------------|----------------------------------------------|-----|

|            | Data Movement                                | 41  |

|            | Addition and Subtraction                     | 44  |

|            | Input and Output                             | 47  |

|            | The Program Shell                            | 49  |

|            | Looping                                      | 50  |

|            | Putting It All Together                      | 53  |

|            | Exercises                                    | 54  |

|            | Answers                                      | 55  |

| CHAPTER 5: | Conditional and Arithmetic Instructions      | 57  |

|            | Arithmetic and the Condition Code Register   | 57  |

|            | The Carry Bit                                | 58  |

|            | The Overflow Bit                             | 61  |

|            | The Zero and Negative Bits                   | 61  |

|            | The Extend Bit                               | 62  |

|            | Comparisons                                  | 62  |

|            | ADDQ and SUBQ Instructions                   | 66  |

|            | Exercises                                    | 68  |

|            | Answers                                      | 69  |

| CHAPTER 6: | Addressing Modes                             | 71  |

|            | Register Direct Modes                        | 72  |

|            | Immediate Data                               | 72  |

|            | Absolute Addressing                          | 73  |

|            | Address Register Indirect                    | 74  |

|            | Address Register Indirect With Postincrement | 77  |

|            | Address Register Indirect With Predecrement  | 79  |

|            | Address Register Indirect With Displacement  | 80  |

|            | Address Register Indirect with Index         | 82  |

|            | Program Counter Relative Modes               | 83  |

|            | Addressing Mode Summary                      | 84  |

|            | Exercises                                    | 85  |

|            | Answers                                      | 86  |

| CHAPTER 7: |                                              | 89  |

|            | Stack Instructions                           | 89  |

|            | Stack Applications                           | 93  |

|            | Exercises                                    | 96  |

|            | Answers                                      | 96  |

| CHAPTER 8: |                                              | 99  |

|            | JSR, BSR, and RTS Instructions               | 99  |

|            | Passing Parameters                           | 102 |

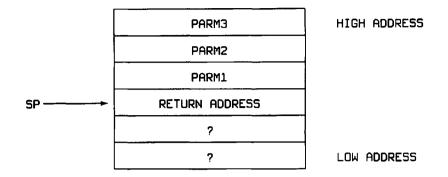

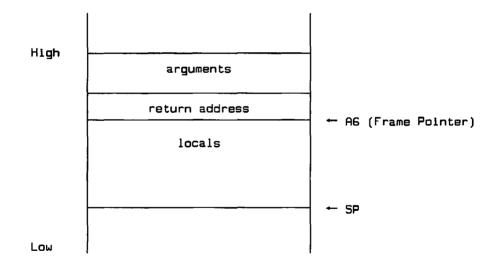

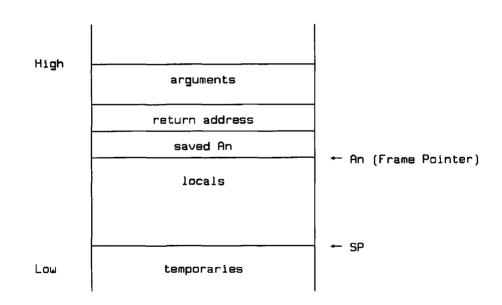

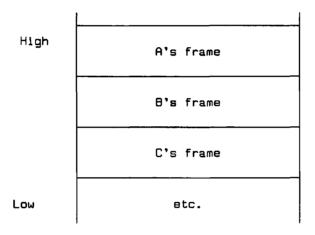

|             | Saving and Restoring the Registers<br>Passing Parameters on the Stack<br>Stack Frames<br>Exercises<br>Answers                                                                                             | 105<br>106<br>109<br>112<br>114                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

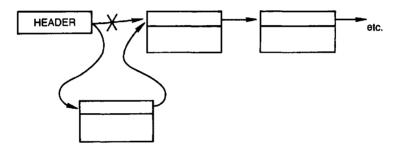

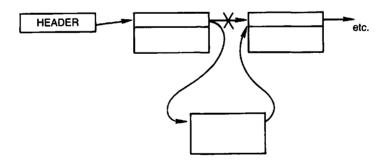

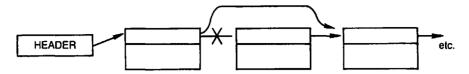

| CHAPTER 9:  | Linked Lists—A Programming Example                                                                                                                                                                        | 117                                                         |

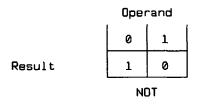

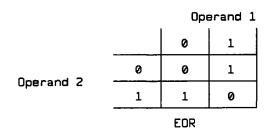

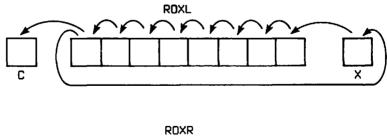

| CHAPTER 10: | Logical, Shift and Rotate Instructions<br>Truth Tables<br>Logical Operations<br>Shifts<br>Rotates<br>Bit Manipulation<br>Exercises<br>Answers                                                             | 129<br>129<br>130<br>132<br>136<br>137<br>138<br>139        |

| CHAPTER 11: | Advanced Arithmetic<br>Multiple Precision Addition and Subtraction<br>Multiplication and Division<br>Decimal Arithmetic<br>Exercises<br>Answers                                                           | 141<br>141<br>145<br>148<br>152<br>153                      |

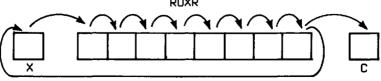

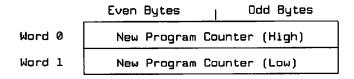

| CHAPTER 12: | Exception Processing, System Control<br>Operations, and I/O<br>The Status Register and System Control<br>Exception Processing<br>Traps<br>Serial I/O<br>Miscelaneous Instructions<br>Exercises<br>Answers | 155<br>155<br>158<br>161<br>163<br>168<br>170<br>171        |

| CHAPTER 13: | The 68010<br>Virtual Memory and the Bus Error Exception<br>Virtual Machines<br>Reference Classifications<br>The Vector Base Register<br>RTD and Loop Mode<br>Summary<br>Exercises<br>Answers              | 173<br>173<br>175<br>177<br>178<br>179<br>181<br>181<br>181 |

| CHAPTER 14: | The 68020                          | 185         |

|-------------|------------------------------------|-------------|

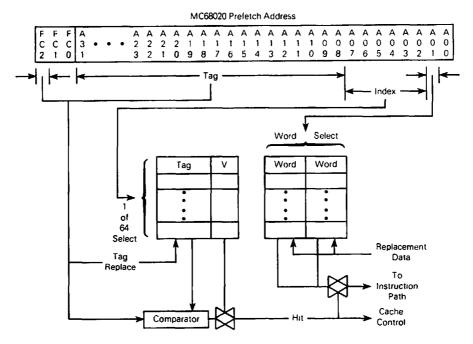

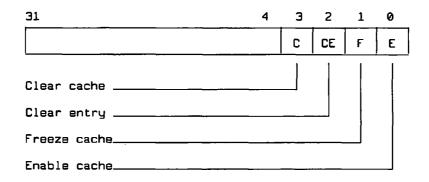

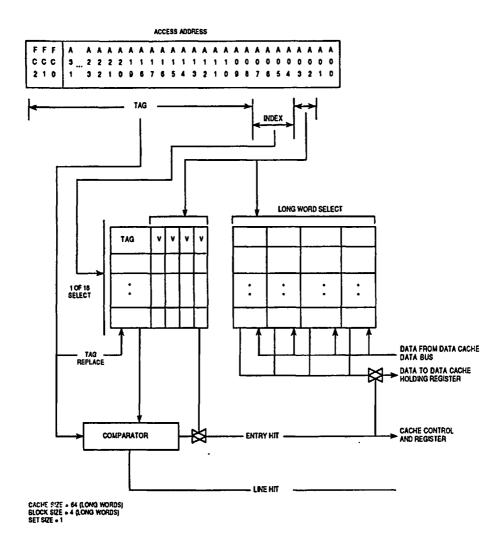

|             | Instruction Caching                | 186         |

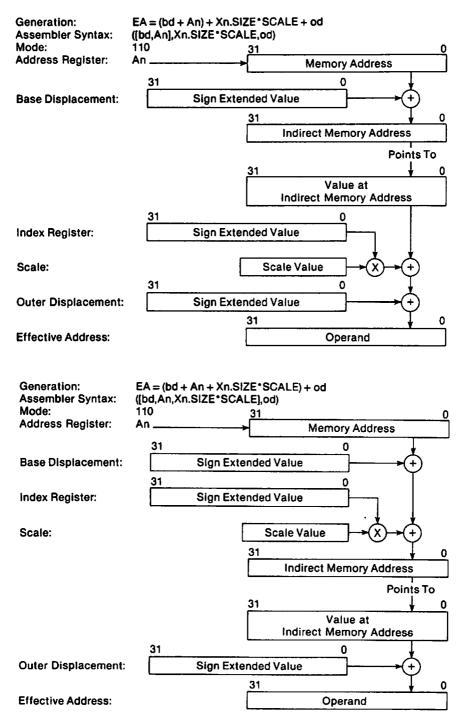

|             | Additional Addressing Modes        | 188         |

|             | Instruction Extensions             | 190         |

|             | New Instructions                   | 193         |

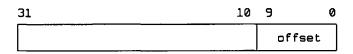

|             | Bit Field Instructions             | 193         |

|             | Breakpoint Instruction             | 193         |

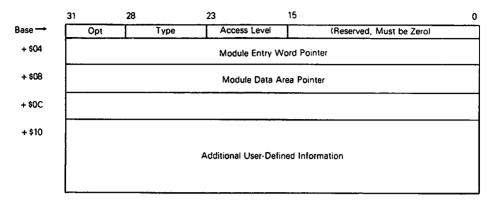

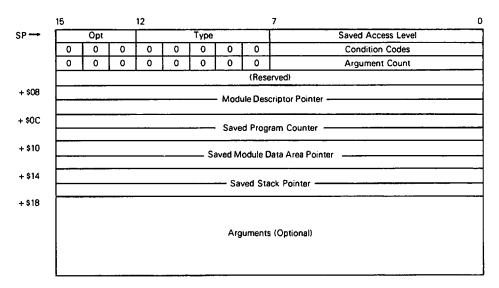

|             | CALLM/RTM                          | 194         |

|             | CAS and CAS2                       | 196         |

|             | CHK2                               | 197         |

|             | CMP2                               | 197         |

|             | Coprocessor Support Instructions   | 197         |

|             | PACK and UNPK                      | 198         |

|             | TRAPcc                             | 199         |

|             | Exercises                          | 1 <b>99</b> |

|             | Answers                            | 200         |

| CHAPTER 15: | The 68030                          | 203         |

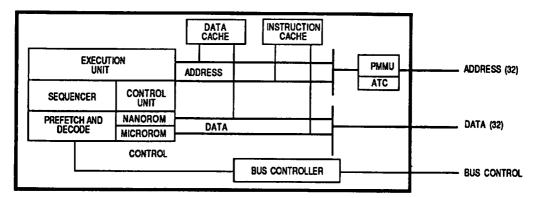

|             | Instruction and Data Caches        | 204         |

|             | Pipelined Architecture             | 206         |

|             | Paged Memory Management            | 206         |

|             | 68030 Instructions                 | 211         |

|             | Exercises                          | 212         |

|             | Answers                            | 212         |

| APPENDIX A: | ASCII Character Codes              | 215         |

| APPENDIX B: | Program Shells and I/O Subroutines | 217         |

| APPENDIX C: | 68000–68020 Instruction Summary    | 229         |

| INDEX       |                                    | 235         |

### INTRODUCTION

Why learn assembly language? Most people do so out of a need to perform programming tasks that are not easy, or not possible, with other languages. The popularity of the 68000 family of microprocessors, as exemplified by the sales figures of the Apple Macintosh, Commodore Amiga, Atari ST, and others, certainly makes it worthwhile to learn more about this line of micros. The particular microprocessor chip your computer uses will remain an abstraction unless you get down to the machine language level; but since no one really programs in machine language, assembly language is the way to gain the most complete knowledge of the 68000 family capabilities.

Programming in assembly language allows the control of every aspect of the computer hardware. Many applications require procedures that are either impossible or inefficient with computer languages such as BASIC. You may be a professional computer user who has a need for a laboratory control computer, such real time applications often require some assembly language programming. Regardless of your reason for learning assembly language, it is challenging and rewarding when your programs start to run. You will feel—and be—"in control."

This book is about programming the 68000 microprocessor, not a particular computer using this chip. For this reason there will be some specifics about your computer and operating system that are not covered. Since you are more than likely experienced in using your computer for other applications, it would be a waste of time to attempt to cover all the small details. Instead, I will present the material in a general manner such that it will be easy to locate the specifics for your particular machine in your manuals. As an aid to those individuals having one of the aforementioned computers, some specific input/output subroutines and a program shell are provided in the appendices.

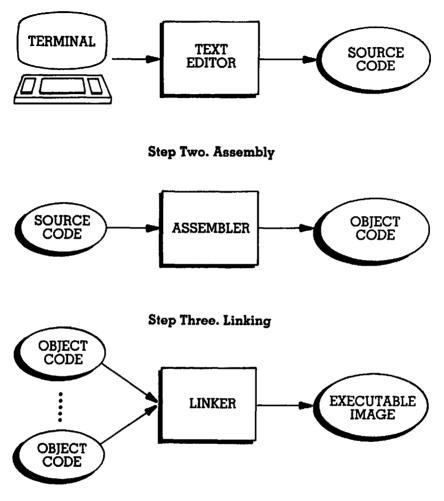

Before we get started, let's pause to review the steps required to write a program and run it. Programming in assembly language, like programming in a high-level language, requires entering the "source code" into the computer. Unless all of your programming has been in BASIC, using its built-in editing features, you have probably used some form of text editor. It really doesn't matter which editor you use as long as you can create a source file for input to the assembler. An assembler is similar to a compiler in that it "translates" a source language into machine language.

The output from an assembler is called the *object code*. Normally this is machine language put into a special format that combines it with other object modules into an *executable image*. This file is essentially a picture of what goes into memory. When you finally run the program, this file is brought into memory so that the microprocessor may execute the instructions.

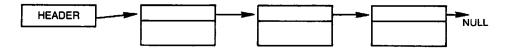

The operation of combining object modules is called *linking*. A special program called a *linker* is used to perform this function. Figure 1 shows the steps used to produce an executable program. The details will differ from computer to computer. Your system may have a program similar to a linker that converts the output of the assembler into an executable form, but does not allow combining object modules. You should have no trouble in learning the commands that perform these steps on a particular machine.

There are quite a few 68000 assemblers available for a range of computer systems. It is not possible to present all the variations in assemblers in this book. Motorola, as the designer of the 68000 microprocessor family, originated its assembly language. The most important task of the assembly language designer is to devise a set of symbolic names for each instruction the microprocessor can execute. These symbolic names are known as *mnemonics*. For example, an instruction to move data from one place to another has the mnemonic MOVE.

In order to allow the greatest flexibility, this book will use the standard Motorola assembler syntax and mnemonics. There will probably be some minor variations with the assembler you use. However, most of the pieces of an assembly language program will be identical regardless of the assembler used, and you should not find it difficult in relating the material to your particular assembler. If you don't presently have an assembler and linker for your computer system, check with the manufacturer, who probably sells a "developer's package" that contains an assembler, a linker, and the system documentation you will need. Many independent software houses also supply development packages. Go to your local computer store and compare these for compatability with the Motorola standard. If the syntax or mnemonics of the assembler are very far from the standard, you should probably consider another one. Other items that are sometimes provided are an editor (a must if you don't have one), an interactive debugger, and other utilities to assist in rapid program development. This book does not assume any specific development aids or utilities.

Step One. Text Editing

Figure 1 Assembler Operation.

In Chapter 1 I will review number systems. If you are an experienced assembly language programmer in another language you probably know most of this material. However, it is a good idea to review the chapter, especially as it presents some details specific to the 68000. •

### NUMBER SYSTEMS

Throughout history mankind has used a variety of methods to represent numerical quantitites. Early man used piles of stones, each stone representing one unit of those items being counted. It soon became obvious that for large numbers, a large number of stones were required. One solution to this problem was to use stones of different sizes. A single large stone could be used to represent a pile of smaller stones. This is similar to the use of the denominations of paper currency. Schemes like this work well for physical entities like coins or stones. However, to represent quantities on paper we would be forced to draw pictures of our piles of stones.

#### Decimal

Our decimal number system is a product of all these schemes. Instead of piles of different numbers of stones or stones of different sizes, the Arabic numerals 0 to 9 and the relative position of these numerals are used to represent the number of stones in a pile and the relative size of the stones. The numerals 0 to 9 can represent quantities from zero to nine. Position can be used to represent any number of sizes. For example, the decimal number "23" can be thought of as representing three small stones and two larger stones. If each larger stone is equivalent to ten small stones, this number represents the equivalent of twenty-three small stones. This may seem obvious to most readers, but it is the basis of all the number systems we will study.

In the decimal number system, each digit's position represents a different power of 10. For example, the number 7458 is equivalent to:

$$7(10)^{3}+4(10)^{2}+5(10)^{1}+8(10)^{0}$$

The choice of 10 as the numerical base, or *radix*, as it is sometimes called, is arbitrary. We can create a number system using any base we desire.

#### **Binary**

Virtually all computers use 2 as the base for numerical quantities. The choice of 2 as a base for computers is not arbitrary. Internally, the electrical elements, or *gates*, that collectively construct the computer are much easier to build if they are required to represent only two values or states, they are thus called *binary* state devices. Each element can only represent the values zero or one. Each one or zero is called a *bit*, or binary digit. In order to represent larger numbers, bit positions must be used. Binary numbers are based on powers of two rather than on powers of ten. For example, the binary number "1011" is equivalent to:

$1(2)^{3}+0(2)^{2}+1(2)^{1}+1(2)^{0}$

This value is equivalent to:

8+0+2+1 = 11

in decimal representation. The positional values of the bits are thus:

```

(2)^{0} = 1

(2)^{1} = 2

(2)^{2} = 4

(2)^{3} = 8

(2)^{4} = 16

.

(2)^{16} = 65,536

.

etc.

```

To convert a binary number to its decimal equivalent, merely add up the appropriate powers of two. If the binary position contains a 1, the decimal value of that bit position is added.

#### Conversions

Converting a decimal number to binary is not quite as simple as converting a binary number to decimal. One method is to work backwards.

We can look for the highest power of two that is not greater than the decimal number, place a 1 in the equivalent bit position, and then subtract this value from the decimal number. We repeat this operation until the number is zero. Bit positions not used in this subtractive process are set to 0. For example, we can convert  $57_{10}$  (57 in base 10) to binary by the following steps:

$57 - 2^5 = 25$   $25 - 2^4 = 9$   $9 - 2^3 = 1$  $1 - 2^0 = 0$  (finished)

This gives us the binary number

$$1(2)^{5}+1(2)^{4}+1(2)^{3}+0(2)^{2}+0(2)^{1}+1(2)^{0} = 111001_{2}$$

Another method can also be used. We can divide the original decimal number by two and check the remainder. If the remainder is one, a binary one is generated. We repeat this division by two until we obtain a zero. This method gives us the bits in reverse. In other words, we get  $2^0$ ,  $2^1$ , and so on. For example, using the same number as above:

```

57/2 = 28 R 1

28/2 = 14 R 0

14/2 = 7 R 0

7/2 = 3 R 1

3/2 = 1 R 1

1/2 = 0 R 1 (finished)

```

Reading the bits in reverse gives us  $111001_2$ , which is the same number as we arrived at before. The method you use is up to you.

These methods can be used to convert from any number base to any other number base. However, the arithmetic must be done in the number base of the number being converted. As this becomes complicated when converting from a system other than decimal, you are better off to convert the number to decimal and then the decimal number to the new base. There are a few exceptions to this rule. One of these exceptions is the conversion of the hexadecimal (hex) base to or from binary. Since hex is used quite extensively with the 68000 family, it is the topic of our next discussion.

#### Hexadecimal

Hexadecimal, or base 16, uses positional values that are powers of 16. Each hex digit can take on 16 values. Since the decimal digits 0 through 9 only represent 10 values, 6 additional symbols are needed. The letters A through F are used to represent these additional values. Thus the hex digits are represented by 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F, corresponding to the values from  $0_{10}$  to  $15_{10}$ . The positional values are:

```

(16)^{0} = 1

(16)^{1} = 16

(16)^{2} = 256

(16)^{3} = 4096

etc.

```

As you can see, these values increase rapidly. A hex number is usually larger than it looks. For example,  $32BF_{10}$  is

$$3(16)^{3}+2(16)^{2}+11(16)^{1}+15(16)^{0}$$

= 12,288+512+176+15 = 12,991<sub>10</sub>

We can convert from decimal to hexadecimal by either method discussed above. For example, to convert  $387_{10}$  to hex, we perform the following:

The result in hex is 183<sub>16</sub>. Remember to list the hex digits in reverse order.

A nice property of hexadecimal numbers is that they can be converted to binary almost by inspection. Since  $2^4=16$ , there is a simple relationship present. Four binary digits grouped together can represent one hexadecimal digit. The binary values 0000 through 1111 represent the hexadecimal digits 0 through F.

| <u>HEX</u> | BINARY HE | <u>K BINARY</u> | •    |

|------------|-----------|-----------------|------|

| 0          | 0000      | 8               | 1000 |

| 1          | 0001      | 9               | 1001 |

| 2          | 0010      | А               | 1010 |

| 3          | 0011      | В               | 1011 |

| 4          | 0100      | С               | 1100 |

| 5          | 0101      | D               | 1101 |

| 6          | 0110      | E               | 1110 |

| 7          | 0111      | F               | 1111 |

To convert from hex to binary we merely write the equivalent of each hex digit in binary. To convert  $6E3C_{16}$  to binary we would write:

6 E 3 C 0110 1110 0011 1100

and our binary equivalent is  $110111000111100_2$ . We can go from binary to hex in the same manner.  $111100001010_2$  is  $FOA_{16}$ .

#### Arithmetic in Binary and Hexadecimal

We can perform the normal arithmetic operations of addition, subtraction, multiplication, and division in any number base. Addition and subtraction are simple if we remember that a carry or borrow may be required. If the sum of two digits equals or exceeds the number base, a carry is generated. The value used as the carry or borrow is equal to the number base. For example, if we add two binary numbers together, we generate a carry if the sum of the bits in one binary position and a possible carry from the next lowest position is greater than or equal to two. Adding  $1100101_2$  to  $0111101_2$  gives us:

```

1100101

+ 0111101

10100010

```

Let's try adding  $72A8_{16}$  to  $1F08_{16}$ .

```

72A8

+ 1F08

----

91B0

```

Subtraction is only slightly more difficult. If the individual digits cannot be subtracted from one another, we need to borrow from the next higher digit position. In other words, if the minuend (top digit) is less than the subtrahend (bottom digit) we need a borrow. In binary the value borrowed is always two. This borrow is added to the minuend, the subtraction is then performed on the two digits. To adjust for the borrow, just as we had to adjust for a carry, we must add one to the subtrahend in the next higher digit position. For example, in binary

| _ | 1111<br>0110 | - | 1001<br>0110 |

|---|--------------|---|--------------|

|   |              |   |              |

|   | 1001         |   | 0011         |

or hexadecimal

55F2 - 4A63 ----0B8F

Hand calculations involving multiplication or division are rarely performed by programmers. However, conventional hand methods can be used. The basic principles we used for addition and subtraction are applied. Although I will not explain multiplication or division, those readers who desire can try some examples and verify their results by converting to decimal and repeating the multiplication or division in the decimal number base.

#### Bits, Bytes, Words and Longwords

So far in our discussion of numbers we have not indicated how large our numbers can be. If you want to write down a very large number on paper, the size of the number is only limited by the size of the paper. This is not the case for computers. Internally the computer must represent numbers by electrical signals. These signals represent the binary values 0 and 1. The maximum size of a number inside the computer is limited to the number of binary digits, or bits, used to represent the number. Theoretically we could use *all* the bits inside the computer to represent a *single* number. This, of course, is not practical. Internally it is convenient to limit the number of bits used for each number.

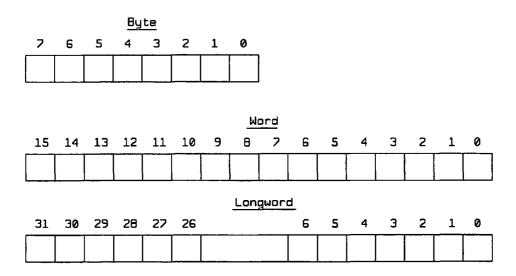

Many computers are organized around groups of eight bits, called *bytes*. The size of memory on many computers is measured in bytes. We might say a computer has 64 thousand bytes of memory. This is equivalent to 512 thousand bits. Modern computers often have memory sizes in the millions of bytes. A megabyte (MB) is equal to approximately one million bytes. As we will discuss shortly, a single byte is normally used to represent a single character of textual information. If we have a 2 MB memory, we can store 2 million characters of information. If we assume approximately 60 characters per line of printed material, and 50 lines per page, this is equivalent to over 650 pages.

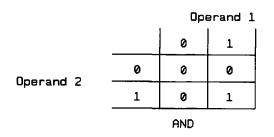

Bytes can be grouped together. For most computers, including the 68000 family, two bytes grouped together form a *word*. A word is therefore equal to 16 bits. This is also equivalent to four hexadecimal digits. We can also have *longwords*, made up of four bytes or 32 bits. Larger groupings are possible but are not normally handled as a single value except by much larger computers. We will be dealing primarily with bytes, words, and longwords in 68000 assembly language programming.

#### **Representing Negative Values**

So far in our discussion of number representations, we have only been dealing with positive numbers. A method of representing negative numbers in the computer must be introduced. You have already learned that numbers are represented internally by binary digits. We must devise a way of including the conventional minus sign "-", used to indicate a negative number, with the number itself. But how does a minus sign translate into binary? Since numbers are either positive or negative, we can indicate this fact by using a single binary digit. A negative number can be indicated by using an "extra" bit rather than a minus sign. This may not work as well on paper, but it is essential for a computer's internal representations.

Numeric quantitites are normally restricted to fixed sizes—a single byte, a word, or some multiple number of words or bytes. It is not practical to append an extra "sign" bit to a fixed unit of storage such as a byte: the central processing unit (CPU) normally is restricted to manipulating integral numbers of bytes, and this extra bit would force the use of an extra complete byte. The solution is to sacrifice one of the bits of our number for use as the sign bit. The size of the largest number we can represent is reduced, but we can now represent the same number of positive numbers as negative numbers.

By convention, if a number is negative we indicate this fact by including a sign bit equal to one. The sign bit is normally the leftmost, or high-order, bit of the number. The simplest technique would be merely to indicate the magnitude of the number in the remaining bits, setting the sign bit to either one or zero to indicate a negative or positive number. This representation, called *sign magnitude*, has been used on older computers. It has a number of disadvantages, the most prominent to a programmer being the fact that both a positive and negative zero exist—both  $10000000_2$  and  $00000000_2$  are zero values for a single byte number. Without going into additional detail, suffice it to say that a better method is needed.

Virtually all modern computers, including microprocessors, use a representation called *two's complement*. The sign bit is still used to indicate whether a number is positive or negative, but the remaining bits do not directly indicate the magnitude of the number if it is a negative number. To represent a negative number in two's complement, we first form the *one's complement* of the number in its binary form. The one's complement is merely the number with all the one bits converted to zeros, and all the zero bits converted to ones. The one's complement of 01100011<sub>2</sub> is 10011100<sub>2</sub>. So far this is quite simple. We are almost finished. To get the two's complement we add one to the one's complement. We perform this addition just as we have done in the previous examples. To complete the conversion of our example, we get:

10011100 + 00000001 ------10011101

Let's convert  $89_{10}$  to  $-89_{10}$  using two's complement. First we must convert  $89_{10}$  to binary.  $89_{10} = 01011001_2$ . Now form the one's complement,  $10100110_2$ ; finally, to get the two's complement we add one. Our result is  $-89_{10} = 10100111_2$ .

The nice property of two's complement numbers is that we can add them together without concern for the sign. We do not have to perform any conversion. As a simple example, we should be able to add  $89_{10}$  and  $-89_{10}$  and obtain a zero result.

| + | 01011001<br>10100111 | <sup>89</sup> 10<br>-89 <sub>10</sub> |

|---|----------------------|---------------------------------------|

|   | 00000000             |                                       |

|   | 00000000             | <sup>0</sup> 10                       |

We ignore any carry out from the sign bit position.

To subtract in two's complement, we merely negate the subtrahend and then add. This operation is performed regardless of whether the subtrahend is positive or negative.

#### **ASCII** Character Codes

In order to represent character information in the computer's memory, we must find a way to convert the such as CR (carriage return), LF (line feed) and HT (horizontal tab). There are other "control character" codes that are of general interest but are not necessarily available on all terminals. For example, a BEL (bell) might sound a beep on your terminal, or a VT (vertical tab) might be implemented. The other codes with values less than  $32_{10}$  are used for a variety of purposes including the protocols used for data communications.

One special character should be mentioned. The DEL (delete) code,  $127_{10}$ , which is sometimes called a *rubout*, is most commonly used by software to indicate the deletion of the last character typed. Some software uses the BS (backspace) character to perform this same operation. You should note that these are really two different character codes,  $8_{10}$  and  $127_{10}$ , and the interpretation as to what, if anything, these characters do is up to the software.

Some computers and terminals have incorporated additional characters as an extension to the standard ASCII character set. By allowing codes above  $127_{10}$ , an additional  $128_{10}$  characters can be specified. These might be from a foreign language, or for special graphics used by certain terminals. The IBM PC, which does not use the 68000, makes extensive use of such an extended character set. You should be aware that these special character sets are not part of the ASCII standard, when you use these codes, your programs will not necessarily be useful on *all* computers, even though they use the 68000 microprocessor.

#### Exercises

a)

- 1. Binary numbers are based on powers of \_\_\_\_

- 2. Give the decimal equivalent of the following binary numbers: a) 11100010 b) 111111 c) 10000000

- 3. Convert the following decimal numbers to binary: a) 126 b) 255 c) 100

- 4. Convert the following binary numbers to hexadecimal: a) 11111111

b) 10000

c) 11000101

- 5. Convert the following hexadecimal numbers to binary: a) 55 b) AB c) EE

- 6. Give the decimal equivalent of the following hexadecimal numbers: a) FF b) 55 c) DE

- 7. Perform the following binary additions:

- a) 110000 b) 01111+ 001111 + 11100

- 8. Perform the following hexadecimal additions:

| FFAA          | b) | 0123          |

|---------------|----|---------------|

| + <u>A100</u> |    | + <u>A5EE</u> |

9. Perform the following binary subtractions:

| a) | 11111    | b) | 11001   |

|----|----------|----|---------|

|    | <u> </u> | -  | - 10000 |

10. Perform the following hexadecimal subtractions:

| a) |   | FFFF | b) |   | 12AA        |

|----|---|------|----|---|-------------|

|    | - | AAAA |    | — | <u>02AB</u> |

- 11. How many bits are there in a byte?

- 12. How many bytes are contained in a 68000 word?

- 13. The 68000 uses what method to represent negative numbers?

- 14. Which bit is the sign bit?

- 15. If a number is negative, what is the binary value of the sign bit?

- 16. Convert the binary number 00111101 to an equivalent negative number.

- 17. What is the decimal equivalent of 11110000 in signed binary?

- 18. What is the equivalent of -100 decimal in a signed hexadecimal byte?

- 19. What number bases are convenient to use when programming the 68000?

- 20. Hexadecimal numbers use what number base?

- 21. What number base is used internally by the 68000?

- 22. Convert the following decimal numbers to binary and hexadecimal:

a) 200 b) 5 c) 65000

- 23. Convert the following unsigned binary numbers to decimal: a) 11010101 b) 00001110 c) 11100000110

- 24. Convert the following unsigned hexadecimal numbers to decimal: a) ABCD b) 123 c) FF

- 25. Convert the following hexadecimal numbers to binary: a) FEAA b) 123A c) 0100

- 26. Convert the following binary numbers to hexadecimal: a) 1100110001 b) 00010000 c)11110111

- 27. Perform the following signed binary additions:

- a) 11111000 + 00111111

- b) 00010001 + 01000000

- c) 11111100 + 00000011

- 28. Perform the following signed binary subtractions:

- a) 11100000 00000001

- b) 00111000 11111111

- c) 10101010 00010101

- 29. What is the range of the ASCII codes that are printable?

- 30. Does the 68000 interpret the ASCII character codes?

#### Answers

1. two 2. a) 226 b) 63 c) 128 3. a) 1111110 b) 11111111 c) 1100100 4. a) FF b) 10 c) C5 5. a) 01010101 b) 10101011 c) 11101110 6. a) 225 b) 85 c) 222 7. a) 111111 b) 101011 8. a) 1A0AA b) A711 9. a) 11010 b) 01001 10. a) 55555 b) OFFF 11.8 12. 2 13. two's complement 14. the high-order bit 15. one 16. 11000011 17. -1618. 9C

19. decimal, binary and hexadecimal 20. 16 21. binary 22. a) 11001000<sub>2</sub>; C8<sub>16</sub> b) 101<sub>2</sub>; 5<sub>16</sub> c) 111110111101000<sub>2</sub>; FDE8<sub>16</sub> 23. a) 213 b) 14 c) 1798 24. a) 43981 b) 288 c) 255 25. a) 1111111010101010 b) 1001000111010 c) 10000000 26. a) 331 b) 10 c) F7 27. a) 100110111 b) 01010001 c) 11111111 28. a) 11011111

- b) 00111001

- c) 10010101

- 29.  $33_{10}$  through  $126_{10}$ , assuming that space,  $32_{10}$ , does not print.

- 30. No. Input/output devices and software interpret the ASCII codes.

•

### MICROCOMPUTER ARCHITECTURE

Before we begin to discuss assembly language, we should take time to explore the world of the microcomputer. Just what is a microcomputer? As the name implies, it is a small computer. This should not mislead you into thinking that a microcomputer cannot be a powerful computing tool. In fact, the microcomputers of today are as powerful as the minicomputers and mainframe computers of just a few years ago. The reduction in size has been a direct consequence of the development of integrated circuits (*chips*) that contain the functional equivalent of many thousands of transistors.

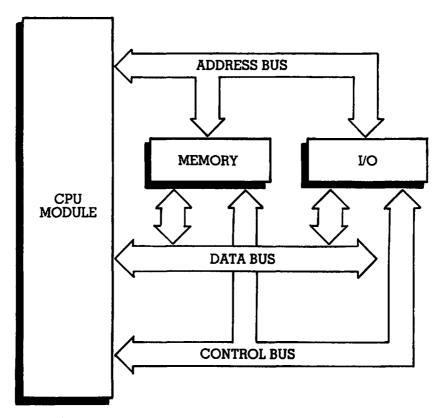

A microprocessor is an integrated circuit that is the basic functional building block of the microcomputer. Figure 2 shows the organization of a basic microcomputer system. The central processing unit (CPU) is the microprocessor chip itself. Electrically connected to the CPU chip is memory. Memory can be of various sizes—for example, over 16 million bytes for the 68000 microprocessor. Also connected to the CPU are input and output (I/O) devices that allow the CPU to communicate with the outside world through a terminal, as well as other information storage devices such as floppy disks and magnetic tapes.

#### The Motorola M68000 Family

The M68000 family of microprocessors is the current step in a continually evolving microprocessor technology. The M68000 family consists of a number of different CPU chips. Among these are the MC68000, MC68008, MC68010, and the MC68020, and the very new MC68030 (actual chips are designated with the prefix MC). Later on in this book I will refer to the M68000 family or the MC68000 CPU chip as just the 68000.

Motorola, like the other major microprocessor designers, didn't start with a chip as sophisticated as the MC68000. Prior to the introduction of the M68000 family, Motorola's bread-and-butter microprocessor line was

Figure 2 Organization of a simple microcomputer system.

the M6800 family. The MC6800 is strictly an 8-bit processor. Motorola attempted to bridge the gap with the MC6809, a pseudo-16-bit CPU. The 6809 never caught on like the Intel 8086 family. However, it did gain wide popularity in the Radio Shack Color computer.

A major issue that faces chip architects is how compatible to make their new chips with earlier chips. It is rarely possible to make a new chip completely compatible, at the machine code level, with prior designs. An alternative is to make the architectures *source code-compatible*. With this scheme, a programmer merely has to reassemble the program for the new chip. He or she is then free to use the features of the new chip in modifications to an already running program. This technique was adopted by Motorola when they jumped to the 6809.

The successor to the Intel 8080 family is the 8086 family. Intel chose to make the new chip family *somewhat* compatible at the source code level. This requirement may have bridled the new architecture to some extent. It is possible to convert an 8080 program to an 8086 program by a source code conversion program. The resulting program can then be modified by hand to allow for the differences in architectures. This scheme did have the advantage that it allowed software vendors to get their products to market quickly. However, the transposed code did not run as well as if it had been written for the target machine in the first place.

Motorola's MACSS (advanced computer system on silicon) project abandoned both object and source code compatibility with the older MC6800 line. While this decision forced a slower introduction of software for the M68000 system family, it allowed a completely unconstrained design. The only concession Motorola made was at the bus interface level: special pinouts are provided to accommodate the large number of 8-bit peripheral chips already in existence. It should be noted that this is a plus, and in no way affects the architecture or, for that matter, the M68000 bus interface.

The question always arises, is a chip 8, 16, 32, or some other number of bits? To properly answer this question requires setting a base of comparison; we must compare apples with apples and oranges with oranges. One basic metric that can be used is the *internal* register size. If 16-bit registers support 16-bit operations with the majority of arithmetic and logical instructions, the chip can be classed as internally a 16-bit architecture. If only a few of the registers and/or instructions are 16-bit, and the remainder are 8-bit, the chip should be classified as an 8-bit chip. The 8080 family is a good example of an 8-bit chip. Another perspective is the width of the data path to and from memory. Contrary to popular belief, the internal size does not have to be the same as the data path; the data path can be larger or smaller. The only restriction is that the data path always be a multiple of a byte (8 bits). The very popular 8088 is an 8-bit data bus version of the 16-bit data bus 8086. This is the chip found in the original IBM PC.

The M68000 family uses a 32-bit architecture internally. It fully supports its 32-bit registers with a rich instruction set performing 32-bit operations. The MC68000 and MC68010 have a 16-bit data bus. The MC68020 and MC68030 have full 32-bit buses. The MC68008 is an 8-bit bus version of the MC68000. Its position is similar to the Intel 8088 in that it allows interfacing to 8-bit buses and memory components.

The astute reader may be asking the question, what effect does the data bus width have on the microprocessor's speed? This is not a simple question to answer. A 16-bit bus does not necessarily allow a CPU to operate twice as fast as an 8-bit bus. It is true, however, that if the CPU desires to fetch a 16-bit value it will require two accesses to memory if an 8-bit bus is used. But even if the 16-bit bus *is* operating at twice the byte transfer rate of the 8-bit bus, there are many other factors that control the CPU speed.

A CPU requires a clock. The speed of this clock determines the inter-

nal rate at which operations are performed. The basic interval between clock pulses is the cycle time for the CPU. It takes a multiple number of cycles for the CPU to execute an instruction. Not all instructions require the same number of cycles, and not every cycle requires an access to memory. Furthermore, the M68000 family supports what is known as an *asynchronous bus:* the speed of the bus does not have to be directly related to the CPU clock. This is a major departure from the M6800 family design.

When you consider this information, together with some more exotic concepts such as instruction prefetch and pipelining, to be covered in later chapters, it is a complicated task to determine the exact relationship between the data bus width and the CPU speed. One thing is clear; the M68000 is a fast microprocessor. Microprocessor manufacturers are constantly designing benchmark tests to show the performance edge of their chips. It is always possible to design a program that shows up the good features of any chip in comparison with others. I will leave it up to you to decide for yourself how much faith you want to place in benchmark programs.

#### The CPU

Before starting on assembly language programming, it is essential that to take a look at the 68000 microprocessor architecture. We are not going to discuss all the details of the actual machine language used by the CPU, but we must know enough about the structure of memory and the internal CPU registers to use assembly language.

As you are probably aware from your experience with a high-level programming language such as BASIC or Pascal, all information in the computer's memory and acted on by the CPU must be represented as numbers. This includes textual information, which is represented by the numeric equivalents for each character as governed by an appropriate character set. You will learn more about character manipulation in later chapters.

The instructions of the 68000 microprocessor are designed to manipulate numeric information in a variety of ways. Data can be moved from one place to another in the computer's memory, or data can be moved from memory to registers contained in the microprocessor chip. Registers are special places to store and manipulate data. They are like memory locations except that they operate at much higher speeds and serve special purposes for the CPU. The most important use of the registers is in performing arithmetic operations. The 68000 is capable of performing the normal arithmetic operations on integer numbers, such as addition, subtraction, multiplication and division, as well as logical operations. Logical operations allow manipulation of the individual bits of the data. You will soon see how logical operations can be very useful.

Some instructions do not manipulate data but are instead used to control the flow of your program. Often you will desire to repeat an operation many times. Rather than repeat the instructions over and over when you write your program, you can use the control instructions to cause the microprocessor to automatically repeat a group of instructions that you have written only once.

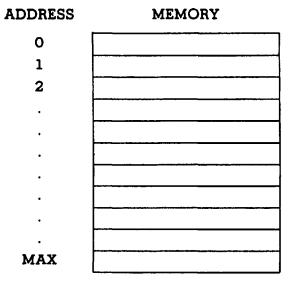

#### Memory

The memory used with the 68000 consists of a number of locations or cells, each holding one 8-bit number or *byte*. Memory cells are numbered from zero up to the maximum allowable amount of memory. The 68000 allows a maximum of 16 megabytes of memory. A megabyte is equal to  $2^{20}$  or 1,048,576<sub>10</sub>. Therefore, 16 megabytes is actually 16,777,216<sub>10</sub> locations or addresses. Figure 3 shows the concept of memory cells and their corresponding addresses.

A program consists of instructions and data. Since everything in memory is a number, careful organization is required to prevent the computer from interpreting instructions as data, or data as instructions. This is normally the responsibility of the programmer.

One of the reasons for using assembly language is to free the program-

Figure 3 Memory Organization.

mer from having to worry about the exact representation of instructions and data in memory. However, a programmer usually finds the occasion when such knowledge is useful.

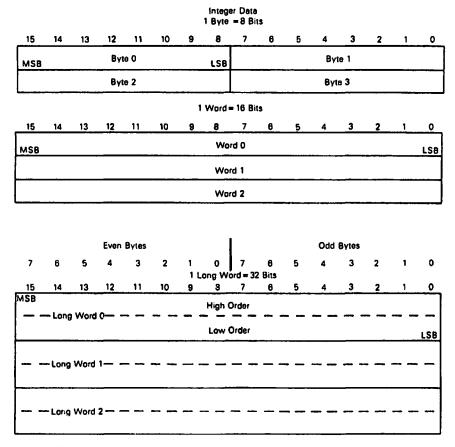

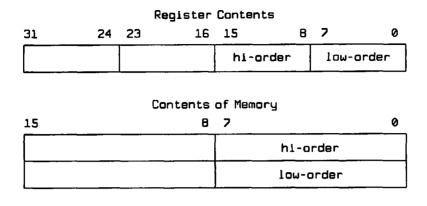

Recall that memory consists of an array of individually addressable bytes. If the data we wish to store in memory is only a single byte, there is no question as to *how* it is represented, only *where*. If, however, the data is a word or instruction consisting of more than one byte, it is not clear how this information is stored. Word data (16 bits) are always stored with the high-order byte stored in the lower memory address. This means that if we were reading a dump of memory, word data would be read directly. Many microprocessors have this order reversed, making it much harder to interpret the contents of memory. Figure 4 shows how byte, word and longword values are stored.

Instructions consist of one or more words. The first word always contains the operation code, or *opcode*. This specifies what the particular

Figure 4 Bytes, words, and longwords memory. (Courtesy of Motorola, Inc.)

instruction is. Many instructions are actually represented by several different opcodes, each specifying a different version of the instruction.

Virtually all systems will have two kinds of memory: *read-only memory* (ROM) and *random-access memory* (RAM). Read-only memory, as its name implies, can be read but not written. How then is it possible to use it? Actually, ROM chips can be written, but not by a program. Certain types of ROM chips have data stored when the chips are manufactured. These ROM chips can never be changed; the data is part of the mask used to create the chips. Other types of ROM chips can be erased, either electrically or using ultraviolet light, and then "reprogrammed." There are special ROM programming devices to do this. ROM's can be used to store a program that will never change. A good example of this is an operating system. All or part of your operating system is more than likely in ROM.

RAM memory is something of a misnomer, since ROM is in fact also a random-access type of memory. By random access we mean that any location in the memory can be accessed in any order, without restriction to a sequential order. Read/write memory actually is what is normally meant by RAM. This is the memory that holds your program and data, as well as data that must be maintained by the operating system. The amount of RAM memory your system has will vary, but some amount of RAM is required with any system. The more RAM memory available, the larger your program and data can be if it is all to fit into memory at the same time.

#### **User and Supervisor Modes**

The 68000 executes programs in one of two modes, *user* or *supervisor*. If a program is running in the user mode, it is most likely a normal everyday program. You will more than likely be writing mostly usermode programs. The supervisor mode is used by programs that require complete control over all aspects of the hardware. Your operating system is a prime example of a program that would run in supervisor mode.

If a program is running in the user mode, it is restricted in a number of ways. Some instructions are designated as privileged. One of these is the STOP instruction. A program in user mode cannot execute any of the privileged instructions. This helps to prevent a program with bugs from crashing the system it is running on. In a multiple user system it is important that one user not be able to do damage to another user. If a user crashes the system, or otherwise performs a privileged instruction, it could affect all users.

While not built into the 68000 CPU chip, many machines have implemented various forms of memory protection. The 68000 provides the user/supervisor mode information on every reference to memory. If the system is so designed, certain areas of memory can be restricted to references only when in the supervisor mode. If a user mode instruction were to try to access this "protected" area of memory, a special condition or "exception" would occur and the operating system could then take control before any damage is done.

#### The CPU Registers

In one sense, a register is a type of memory location. However, it is located right on the CPU chip itself. Registers differ from conventional memory locations in that they operate at a higher speed. In other words, if we use registers in a calculation, it will be faster to perform than if memory locations were used. Additionally, registers are specified by special names rather than just by numbers. The existence of a good register set is a major asset to the architecture of a particular microprocessor. The 68000 family is a good example of a microprocessor with a rich register set.

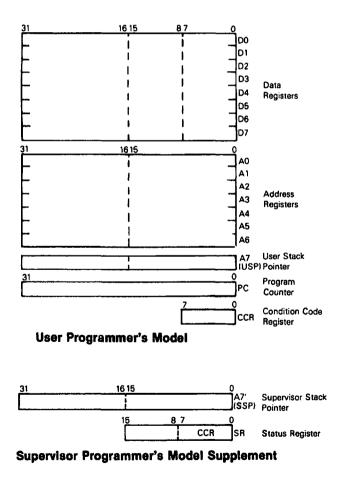

Depending on whether a program is running in user or supervisor mode, there is a slightly different view of the CPU registers. This view is known as the *programmer's model*. The following paragraphs discuss the programmer's model for the user mode.

The 68000 has sixteen 32-bit general-purpose registers. These are divided into two groups of eight. The eight data registers, D0 through D7, are the registers you would normally use to perform arithmetic operations. These can be used as bytes, words, or longwords. The second group of eight general-purpose registers are the address registers, A0 through A7. These registers can be used for arithmetic operations, but are primarily designed for use in the special *addressing modes* discussed in subsequent chapters. The address registers can be used as words or longwords, but not as bytes. In the next chapter you will learn more of the details concerning the use of the sixteen general-purpose registers.

Address register A7, also known as the user stack pointer (USP), has a special interpretation by the 68000. Some instructions affect this register without its being explicitly specified. You will learn all about stacks and the use of the USP in Chapter 7. For now, consider it as just one of the eight address registers.

Another very important register is the *program counter*, or PC. This 32-bit register is used to hold the memory address of the next instruction that the CPU will execute. The programmer never explicitly references this register; its contents are always updated by the CPU. Normally, the PC advances as the program executes sequential instructions that are in

memory. If an instruction causes a branch to a part of the program other than the next sequential instruction, the PC will be updated automatically.

The final register in the user programmer's model is the *condition* code register, or CCR. This is an 8-bit register that contains individual bits that are set or reset as the result of arithmetic instructions. The CCR will be covered in detail in Chapter 5.

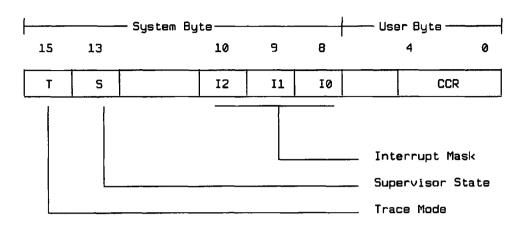

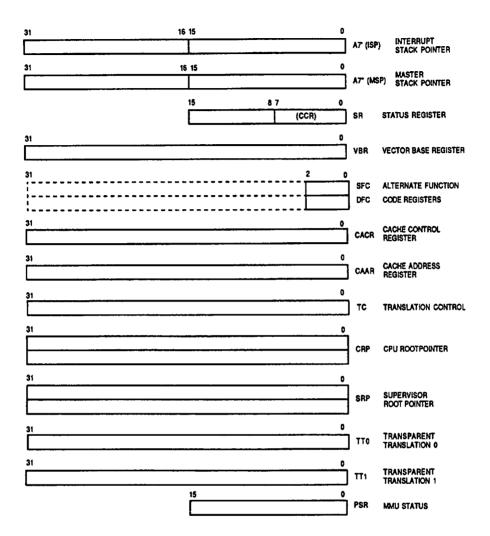

The supervisor programmer's model is identical to the user mode programmer's model with two exceptions. First, in the supervisor mode there is a different register A7, known as the *supervisor stack pointer*, or SSP. This register is totally distinct from the USP. Second, the condition code register is still present, but it is in a 16-bit form. Together with the new high-order 8 bits, it is known as the *status register*, or SR. Figure 5 shows the programmer's models for both the user and supervisor modes.

Figure 5 Programmer's models. (Courtesy of Motorola, Inc.)

#### Input/Output

It may come as a surprise to you that the 68000 does not have any input/output instructions. How then, is I/O performed? The 68000 family uses a technique known as *memory mapped I/O*. This means that input/output devices are connected to the system via interface chips that are connected to the CPU as if they were areas of memory. A small part of the huge amount of memory we are allowed must be sacrificed; it is now used for I/O and can't be used for main memory at the same time. The real advantage to the memory-mapped I/O technique is that rather than being restricted to a small number of special I/O instructions, we can use *all* of the 68000 memory reference instructions with I/O devices.

A large variety of I/O interface chips are available for the 68000 family. A number of these were formerly used with the M6800 family. The 68000 allows the use of these 8-bit chips as well as the newer 16-bit I/O devices specifically designed for the 68000. In Chapter 12 we will discuss the programming of a typical I/O chip. We will use an asynchronous serial I/O device or UART chip.

#### Exercises

- 1. What are the three main parts of a microcomputer?

- 2. What is the difference between the MC68000 and the MC68008?

- 3. What is the newest member of the M68000 family?

- 4. Is the M68000 family an extension of the M6800 architecture?

- 5. How many bits is the internal architecture of the 68000?

- 6. What are the data bus sizes for the M68000 family?

- 7. Is the M68000 data bus synchronous or asynchronous?

- 8. What is the difference between RAM and ROM?

- 9. What is the purpose of supervisor mode?

- 10. Are registers faster or slower than memory?

- 11. How much memory is allowed with the MC68000?

- 12. What are the 32-bit general-purpose registers?

- 13. Is multi-byte data stored with the high order byte in the lowest or highest address?

- 14. Are all instructions the same number of words?

- 15. What is the purpose of the program counter?

- 16. What register is used for the USP and SSP?

- 17. How many input/output instructions does the 68000 have?

# Answers

- 1. CPU, memory, and I/O.

- 2. The MC68000 transfers two bytes of data to and from memory, while the MC68008 only transfers one byte.

- 3. The MC68030.

- 4. No.

- 5. 32 bits.

- 6. The MC68000 and the MC68010 are 16-bit buses, while the MC68020 and the MC68030 are 32-bit buses.

- 7. Asynchronous.

- 8. RAM can be read and written, while ROM can only be read.

- 9. Supervisor mode allows the design of operating systems that can make it more difficult for a user's program to crash the system.

- 10. Much faster.

- 11. 16 megabytes.

- 12. D0-D7 and A0-A7.

- 13. The lowest.

- 14. No, an instruction can be one or more words. The first word is the opcode word.

- 15. The PC contains the addresses of the instructions as they are executed.

- 16. A7.

- 17. None; memory-mapped I/O is used.

# ASSEMBLER SOURCE FORMAT

There are many assemblers available for the 68000 family. They differ from each other in minor ways. It would be virtually impossible to present the details of every assembler on the market. Rather, I will present what is a relatively standard core, based on the specifications provided by Motorola for its assemblers. There are many assembler features that are left out. A careful reading of your assembler manual will provide these details. What is presented here is enough information to get you programming in 68000 assembler. You should, however, verify that your assembler is compatible with this core.

The assembler processes the source program line by line. A line of the source program can be translated into a machine instruction, or generate an element or elements of data to be placed in memory; or the line may only provide information to the assembler itself. The lines of the source program are sometimes referred to as *source statements*.

Regardless of the use of a particular line of the source program, the format of each line is relatively standard. The general format of a source line consists of four fields, as follows:

[<label>] <operation> [<operand>] [<comment>]

Not all of the four fields must appear on all lines; brackets [] have been used to indicate fields that are optional. The comment field is always optional, but the label and/or operand fields may be required depending on the contents of the operation field. Unless a source line consists solely of a comment, the operation field is required. If a line is to consist only of a comment, the first character on the line must be an asterisk (\*). This must appear in the leftmost position on the line, column 1. The remainder of the line is ignored by the assembler.

A field consists of one or more *tokens*. A token is the smallest meaningful unit of information that the assembler uses. Tokens are identifiers or numeric constants. The symbolic names of the machine instructions are an example of identifiers. The fields of a source line are separated by one or more spaces. All 68000 assemblers recognize the space character as a field separator; most assemblers also recognize the tab character as a field separator, and treat it as a space. Generally, where one space or tab is allowed, you may also use more than one. You must be careful not to insert a space in the middle of a field, as this causes the assembler to treat the next non-blank characters as the next field.

A *delimiter* is a special character that can serve to mark the end of a token, besides having its own special meaning. Punctuation characters such as commas, periods, and colons are examples of delimiters.

Figure 6 is an excerpt from a sample program that we will use to further discuss the format of assembler source lines. As you can see, the program consists mainly of character sequences that look like English language words separated by punctuation. These character sequences are the *identifiers*. The rules for creating identifiers varies slightly from assembler to assembler, but the following rules work with almost every assembler:

- 1. The first character must be alphabetic (A...Z, a...z).

- 2. Any additional characters may be alphabetics or digits (0...9).

- 3. Only the first eight characters are significant; the rest are ignored.

There are a number of variations from these rules. Some assemblers retain significance for more than eight characters. Others treat the upperand lower-case alphabetic characters as equivalent, or retain uniqueness, or allow only the use of one case. For example, "COUNT" and "count" may be completely different identifiers. Generally, assemblers allow instructions and directives to be in either case. Characters other than the alphanumerics are sometimes allowed. Check your assembler manual to be sure. Throughout this book we will use upper case, and be careful not to mix cases.

#### The Label Field

The label field always contains a symbol formed with the standard rules for identifiers. If a label is present, it is used to associate the symbol with a value. This value may represent the location of data in memory, a constant, or the location in memory of the instruction in the operation field.

Labels can be used to locate data, such as a variable, stored at particular locations in memory. A variable consists of one or more bytes. Normally variables will be bytes, words, or longwords. It is important to reserve sufficient space for a variable. If an instruction tries to place a longword of data at a memory location only large enough to hold a word, the data will overwrite a part of memory that it shouldn't.

| *PROGRAM TO ECHO A LINE |               |                                                          |                                                                                                                   |

|-------------------------|---------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| *                       | TEXT          |                                                          |                                                                                                                   |

| START:                  | LEA           | BUFFER, AO                                               | INITIALIZE BUFFER POINTER<br>GET A CHARACTER                                                                      |

| LOOP:                   | JSR           | GETC                                                     | GET A CHARACTER<br>SAVE CHARACTER IN BUFFER                                                                       |

|                         | MOVE.B        | D0, (A0) +                                               | SAVE CHARACTER IN BUFFER                                                                                          |

|                         | CMPT.R        | #CR.D0                                                   | END OF LINE?                                                                                                      |

|                         | BNE           | LOOP                                                     | NEXT CHARACTER                                                                                                    |

|                         | LEA           | BUFFER,A0                                                | RESET BUFFER POINTER                                                                                              |

|                         | JSR           | NEWLINE                                                  | NEXT CHARACTER<br>RESET BUFFER POINTER<br>GO TO A NEW LINE<br>GET A CHARACTER<br>OUTPUT TO SCREEN<br>END OF LINES |

| LOOP2:                  | MOVE.B        | (A0) + , D0                                              | GET A CHARACTER                                                                                                   |

|                         | JSR           | PUTC                                                     | OUTPUT TO SCREEN                                                                                                  |

|                         | CWLI'B        | #CK,DU                                                   | END OF LINE?                                                                                                      |

|                         | BNE           | LOOP2                                                    | GET NEXT CHARACTER<br>GO TO NEW LINE<br>RETURN TO SYSTEM<br>"                                                     |

| PINI.                   | JSK<br>MOVE W | #0 = (SD)                                                | CO IO NEW DINE                                                                                                    |

| LTNT:                   |               | #0,-(SF)<br>#1                                           | n                                                                                                                 |

| *                       | INAF          | <b>н т</b>                                               |                                                                                                                   |

| PUTC:                   | MOVEM .L      | D0 - D7 / A0 - A6 - (S)                                  | P) SAVE REGISTERS                                                                                                 |

|                         | ANDI.L        | #\$FF,D0                                                 | MAKE SURE WE HAVE ONLY A BYTE                                                                                     |

|                         | MOVE.W        | D0,-(SP)                                                 | MAKE SURE WE HAVE ONLY A BYTE OUTPUT TO OP. SYS.                                                                  |

|                         | MOVE.W        | #2,-(SP)                                                 | n                                                                                                                 |

|                         | TRAP          | #1<br>#4,SP                                              | n                                                                                                                 |

|                         | ADDQ.L        | #4,SP                                                    | CLEAN UP STACK                                                                                                    |

|                         |               | (SP) + , DU - D7 / AU - AU | A6 RESTORE REGISTERS                                                                                              |

| *                       | RTS           |                                                          | RETURN                                                                                                            |

|                         | MOVEM . L     | D1 - D7 / A0 - A6 = (S1)                                 | P) SAVE REGISTERS                                                                                                 |

| 0510.                   |               |                                                          | GET A CHAR. FROM OP. SYS.                                                                                         |

|                         | ጥጽልዖ          | #1                                                       | a                                                                                                                 |

|                         | ANDI.L        | #\$7F,D0<br>#2,SP                                        | MASK TO 7 BITS                                                                                                    |

|                         | ADDQ.L        | #2,SP                                                    | CLEAN UP STACK                                                                                                    |

|                         | MOVEM.L       | (SP)+,D1-D7/A0-2                                         | A6 RESTORE REGISTERS                                                                                              |

|                         | RTS           |                                                          | RETURN                                                                                                            |

| *                       | BOU           | ¢0.D                                                     |                                                                                                                   |

| CR:                     | EQU<br>EQU    | \$0D                                                     | CARRIAGE RETURN                                                                                                   |

| LF:<br>*                | FÕO           | γUA                                                      | LINE FEED                                                                                                         |

|                         | MOVE . L      | D0, -(SP)                                                | SAVE DO                                                                                                           |

|                         |               | #CR,D0                                                   | OUTPUT A CR                                                                                                       |

|                         | JSR           | PUTC                                                     | n                                                                                                                 |

|                         | MOVE.B        | #LF,D0                                                   | OUTPUT A LF                                                                                                       |

|                         | JSR           | PUTC                                                     | 11                                                                                                                |

|                         | MOVE.L        | (SP) + , D0                                              | RESTORE DO                                                                                                        |

|                         | RTS           |                                                          | RETURN                                                                                                            |

| *                       |               |                                                          |                                                                                                                   |

| *                       | DATA          |                                                          |                                                                                                                   |

| BUFFER:                 |               | 100                                                      | 100 CHARACTER BUFFER                                                                                              |

| BUFFEK:                 | END           | 100                                                      | INA CUMRACIER BULLER                                                                                              |

|                         | 2             |                                                          |                                                                                                                   |

.

Figure 6 Sample program.

A symbol in the label field can be made to equal a numeric constant. Anywhere this symbol appears in your program it is interpreted as if you wrote the constant itself. For example, you could define the symbol MAX to represent the constant 1000.

A symbol in the label field can also be used to specify the memory location of an instruction. This is a true label. Although the first field is called the label field, only the symbols that are present in the label field of a source line that translates into a memory location are the true labels of a 68000 assembly language program. Unless a label starts in column 1, it must be delimited with a semicolon. In the latter case, the label can start in any column as long as it is the first thing on the line.

#### The Operation Field

The operation field contains either a machine instruction or an assembler directive. Each machine instruction has a special symbol or *mnemonic* associated with it. If a particular machine instruction is desired, the proper mnemonic must be placed in the operation field. Assembler directives have symbolic names that are different from the machine instructions. The assembler is thus able to differentiate between a machine instruction and a directive.

If a machine instruction is placed in the operation field, the assembler will generate the appropriate words to be placed in memory corresponding to the translation of the source statement. Assembler directives may or may not generate bytes to be stored in memory. Some directives merely control the format of the assembly listing, or provide other information about the program. Directives are also used to define symbols.

#### The Operand Field

Many machine instructions as well as assembler directives require one or more *operands*. The operand field is used to provide these operands. Individual operands can consist of constants, variables, or special symbols. Expressions made up of constants, variables, and special symbols are also permitted. The rules for making up expressions vary slightly from assembler to assembler. Standard arithmetic expressions such as

COUNT+5

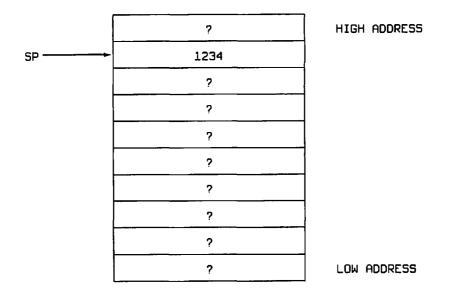

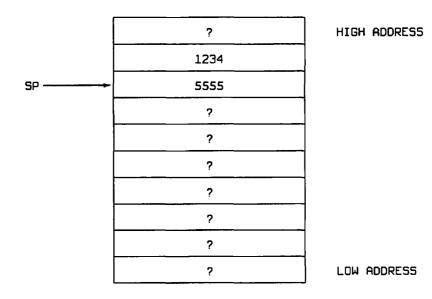

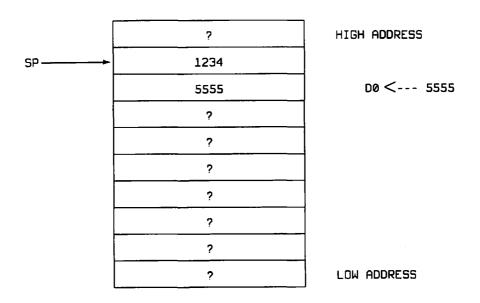

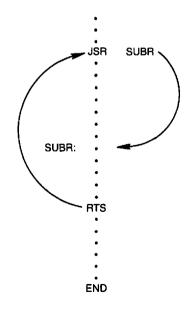

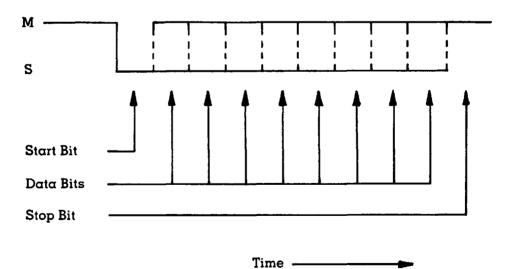

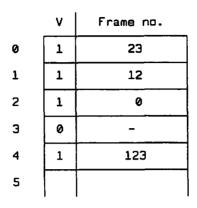

are allowed by all assemblers. The characters +, -,  $\bullet$ , and / are interpreted as addition, subtraction, multiplication, and division respectively. Most assemblers allow the use of parentheses in arithmetic expressions. Consult your assembler manual for details on expression evaluation.